Physikalisches Design (Elektronik) - Physical design (electronics)

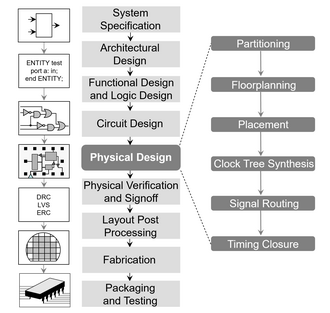

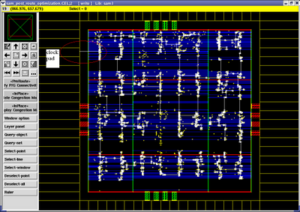

Beim Entwurf integrierter Schaltkreise ist der physikalische Entwurf ein Schritt im Standardentwurfszyklus, der nach dem Entwurf der Schaltung folgt . In diesem Schritt werden Schaltungsdarstellungen der Komponenten (Geräte und Verbindungen) des Entwurfs in geometrische Darstellungen von Formen umgewandelt, die, wenn sie in den entsprechenden Materialschichten hergestellt werden, das erforderliche Funktionieren der Komponenten sicherstellen. Diese geometrische Darstellung wird als integriertes Schaltungslayout bezeichnet . Dieser Schritt ist normalerweise in mehrere Unterschritte unterteilt, die sowohl das Design als auch die Überprüfung und Validierung des Layouts umfassen.

Das moderne IC-Design ( Integrated Circuit ) wird mithilfe von HDLs und Back-End-Design oder physikalischem Design in Front-End - Design unterteilt . Die Eingaben für das physische Design sind (i) eine Netzliste, (ii) Bibliotheksinformationen zu den Grundgeräten im Design und (iii) eine Technologiedatei, die die Herstellungsbeschränkungen enthält. Das physische Design wird normalerweise durch die Layout-Nachbearbeitung abgeschlossen , bei der Änderungen und Ergänzungen des Chip-Layouts vorgenommen werden. Darauf folgt der Herstellungs- oder Herstellungsprozess, bei dem Entwürfe auf Siliziumchips übertragen werden, die dann in ICs verpackt werden.

Jeder der oben genannten Phasen sind Entwurfsabläufe zugeordnet. Diese Entwurfsabläufe legen den Prozess und die Richtlinien / Rahmenbedingungen für diese Phase fest. Der physische Entwurfsablauf verwendet die Technologiebibliotheken, die von den Fertigungshäusern bereitgestellt werden. Diese Technologiedateien enthalten Informationen zum Typ des verwendeten Siliziumwafers, den verwendeten Standardzellen, den Layoutregeln (wie DRC in VLSI) usw.

Abteilungen

In der Regel wird das physische IC-Design in vollständig benutzerdefiniertes und semi-benutzerdefiniertes Design unterteilt.

- Vollständig benutzerdefiniert: Designer bietet volle Flexibilität beim Layoutdesign. Es werden keine vordefinierten Zellen verwendet.

- Semi-Custom: Es werden vorgefertigte Bibliothekszellen (vorzugsweise mit DFM getestet ) verwendet. Der Designer hat Flexibilität bei der Platzierung der Zellen und beim Routing.

Man kann ASIC für Full Custom Design und FPGA für Semi-Custom Design Flows verwenden. Der Grund dafür ist, dass man die Flexibilität hat, Entwurfsblöcke aus vom Hersteller bereitgestellten Bibliotheken in ASIC zu entwerfen / ändern. Diese Flexibilität fehlt für Semi-Custom-Flows mit FPGAs (z . B. Altera ).

ASIC-Entwurfsablauf

Die Hauptschritte im physischen Entwurfsablauf des ASIC sind:

- Design Netlist (nach der Synthese)

- Bodenplanung

- Partitionierung

- Platzierung

- Uhrbaumsynthese (CTS)

- Routing

- Physische Überprüfung

- Layout-Nachbearbeitung mit Maskendatengenerierung

Diese Schritte sind nur die Grundlagen. Es gibt detaillierte PD-Flows, die abhängig von den verwendeten Tools und der Methodik / Technologie verwendet werden. Einige der im Back-End-Design verwendeten Tools / Software sind:

- Cadence (Cadence Encounter RTL-Compiler, Encounter Digital Implementation, Cadence Voltus IC-Leistungsintegritätslösung, Cadence Tempus Timing Signoff-Lösung)

- Synopsys (Design Compiler, IC Compiler II, IC Validator, PrimeTime, PrimePower, PrimeRail)

- Magma (BlastFusion usw.)

- Mentor Graphics (Olympus SoC, IC-Station, Kaliber)

Der physische ASIC-Entwurfsablauf verwendet die Technologiebibliotheken, die von den Fertigungshäusern bereitgestellt werden. Technologien werden üblicherweise nach minimaler Strukturgröße klassifiziert. Standardgrößen in der Größenordnung der Miniaturisierung sind 2 & mgr; m, 1 & mgr ; m, 0,5 & mgr; m, 0,35 & mgr; m, 0,25 & mgr; m, 180 nm , 130 nm, 90 nm, 65 nm, 45 nm, 28 nm, 22 nm, 18 nm, 14 nm usw. Sie können auch klassifiziert werden gemäß den wichtigsten Herstellungsansätzen: n-Well-Prozess, Twin-Well-Prozess, SOI- Prozess usw.

Netzliste entwerfen

Das physikalische Design basiert auf einer Netzliste, die das Endergebnis des Synthesevorgangs ist. Synthesis konvertiert das RTL-Design, das normalerweise in VHDL oder Verilog HDL codiert ist, in Beschreibungen auf Gate-Ebene, die die nächsten Tools lesen / verstehen können. Diese Netzliste enthält Informationen zu den verwendeten Zellen, ihren Verbindungen, dem verwendeten Bereich und anderen Details. Typische Synthesewerkzeuge sind:

- Cadence RTL Compiler / Build Gates / Physikalisch kenntnisreiche Synthese (PKS)

- Synopsys Design Compiler

Während des Synthesevorgangs werden Einschränkungen angewendet, um sicherzustellen, dass das Design die erforderliche Funktionalität und Geschwindigkeit (Spezifikationen) erfüllt. Erst nachdem die Netzliste auf Funktionalität und Timing überprüft wurde, wird sie für den physischen Entwurfsablauf gesendet.

Schritte

Bodenplanung

Der zweite Schritt im physischen Entwurfsablauf ist die Bodenplanung . Unter Bodenplanung versteht man den Prozess, Strukturen zu identifizieren, die nahe beieinander platziert werden sollten, und ihnen Platz zuzuweisen, um die manchmal widersprüchlichen Ziele des verfügbaren Platzes (Kosten des Chips), der erforderlichen Leistung und des Wunsches nach Nähe zu erfüllen zu allem anderen.

Basierend auf dem Bereich des Entwurfs und der Hierarchie wird ein geeigneter Grundriss festgelegt. Die Grundrissplanung berücksichtigt die im Design verwendeten Makros, den Speicher, andere IP-Kerne und deren Platzierungsanforderungen, die Routing-Möglichkeiten und auch den Bereich des gesamten Designs. Die Bodenplanung bestimmt auch die E / A-Struktur und das Seitenverhältnis des Entwurfs. Ein schlechter Grundriss führt zu einer Verschwendung der Matrizenfläche und einer Überlastung des Routings.

In vielen Entwurfsmethoden sind Fläche und Geschwindigkeit Gegenstand von Kompromissen. Dies ist auf begrenzte Routing-Ressourcen zurückzuführen. Je mehr Ressourcen verwendet werden, desto langsamer ist der Vorgang. Durch die Optimierung auf minimale Fläche kann das Design sowohl weniger Ressourcen verbrauchen als auch die Abschnitte des Designs näher beieinander liegen. Dies führt zu kürzeren Verbindungsentfernungen, weniger verwendeten Routing-Ressourcen, schnelleren End-to-End-Signalpfaden und noch schnelleren und konsistenteren Orts- und Routenzeiten. Richtig gemacht, gibt es keine Nachteile bei der Grundrissplanung.

In der Regel profitieren Datenpfadabschnitte am meisten von der Grundrissplanung, wohingegen Zufallslogik, Zustandsautomaten und andere nicht strukturierte Logik sicher dem Placer-Abschnitt der Orts- und Routensoftware überlassen werden können.

Datenpfade sind typischerweise die Bereiche des Entwurfs, in denen mehrere Bits parallel verarbeitet werden, wobei jedes Bit auf die gleiche Weise modifiziert wird, wobei möglicherweise ein gewisser Einfluss benachbarter Bits besteht. Beispielstrukturen, aus denen Datenpfade bestehen, sind Addierer, Subtrahierer, Zähler, Register und Muxes.

Partitionierung

Beim Partitionieren wird der Chip in kleine Blöcke unterteilt. Dies geschieht hauptsächlich, um verschiedene Funktionsblöcke zu trennen und um die Platzierung und das Routing zu vereinfachen. Die Partitionierung kann in der RTL-Entwurfsphase erfolgen, wenn der Konstrukteur den gesamten Entwurf in Unterblöcke unterteilt und dann mit dem Entwurf jedes Moduls fortfährt. Diese Module sind im Hauptmodul TOP LEVEL miteinander verbunden. Diese Art der Partitionierung wird allgemein als logische Partitionierung bezeichnet. Das Ziel der Partitionierung besteht darin, die Schaltung so aufzuteilen, dass die Anzahl der Verbindungen zwischen Partitionen minimiert wird.

Platzierung

Vor Beginn der Platzierungsoptimierung werden alle Drahtlastmodelle (WLM) entfernt. Die Platzierung verwendet RC-Werte von Virtual Route (VR), um das Timing zu berechnen. VR ist der kürzeste Manhattan-Abstand zwischen zwei Pins. VR-RCs sind genauer als WLM-RCs.

Die Platzierung erfolgt in vier Optimierungsphasen:

- Optimierung vor der Platzierung

- Bei der Platzierungsoptimierung

- Post-Placement-Optimierung (PPO) vor der Clock-Tree-Synthese (CTS)

- PPO nach CTS.

- Die Optimierung vor der Platzierung optimiert die Netzliste vor der Platzierung. HFNs (High Fanout Nets) werden reduziert. Es kann auch die Zellen verkleinern.

- Die In-Placement-Optimierung optimiert die auf VR basierende Logik neu. Dies kann die Größenbestimmung von Zellen, das Verschieben von Zellen, das Umgehen von Zellen, das Aufteilen von Netzen, das Duplizieren von Gates, das Einfügen von Puffern und die Wiederherstellung von Bereichen durchführen. Die Optimierung führt eine Iteration der Setup-Korrektur, des inkrementellen Timings und der überlastungsbedingten Platzierung durch.

- Optimierung nach der Platzierung, bevor CTS die Netzlistenoptimierung mit idealen Uhren durchführt. Es kann Setup-, Hold- und Max Trans / Cap-Verstöße beheben. Es kann eine Platzierungsoptimierung basierend auf globalem Routing durchführen. Es führt eine HFN-Synthese durch.

- Die Optimierung nach der Platzierung nach CTS optimiert das Timing mit der propagierten Uhr. Es wird versucht, den Zeitversatz beizubehalten.

Uhrbaumsynthese

Das Ziel der Taktbaumsynthese ( CTS ) besteht darin, den Versatz und die Einfügungsverzögerung zu minimieren. Die Uhr wird nicht vor CTS weitergegeben, wie in der Abbildung gezeigt. Nach dem CTS-Hold sollte sich der Durchhang verbessern. Der Taktbaum beginnt an der von .sdc definierten Taktquelle und endet an den Stoppstiften des Flops. Es gibt zwei Arten von Stopp-Pins, die als Ignorier-Pins und Sync-Pins bezeichnet werden. "Nicht berühren" -Schaltungen und Pins im Front-End (Logiksynthese) werden als "Ignorieren" -Schaltungen oder Pins am Back-End (physikalische Synthese) behandelt. "Ignorieren" -Pins werden für die Timing-Analyse ignoriert. Wenn die Uhr geteilt ist, ist eine separate Versatzanalyse erforderlich.

- Der globale Versatz erreicht einen Nullversatz zwischen zwei synchronen Pins, ohne die logische Beziehung zu berücksichtigen.

- Der lokale Versatz erreicht einen Nullversatz zwischen zwei synchronen Pins unter Berücksichtigung der logischen Beziehung.

- Wenn die Uhr absichtlich schief gestellt wird, um das Setup-Spiel zu verbessern, spricht man von einem nützlichen Versatz.

Starrheit ist der Begriff, der in Astro geprägt wird, um die Lockerung von Zwängen anzuzeigen. Je höher die Steifigkeit, desto strenger sind die Einschränkungen.

Bei der Taktbaumoptimierung (CTO) kann die Uhr abgeschirmt werden, damit das Rauschen nicht mit anderen Signalen gekoppelt wird. Durch die Abschirmung wird die Fläche jedoch um 12 bis 15% vergrößert. Da das Taktsignal globaler Natur ist, wird dieselbe Metallschicht, die für das Stromrouting verwendet wird, auch für den Takt verwendet. CTO wird durch Pufferdimensionierung, Gate-Dimensionierung, Pufferverlagerung, Pegelanpassung und HFN-Synthese erreicht. Wir versuchen, den Setup-Durchhang bei der Optimierung vor, bei der Platzierung und nach der Platzierung vor den CTS-Phasen zu verbessern, während wir den Durchhang beim Halten vernachlässigen. Bei der Optimierung nach der Platzierung nach dem CTS wird das Halten des Durchhangs verbessert. Infolge von CTS werden viele Puffer hinzugefügt. Im Allgemeinen werden für 100.000 Tore ca. 650 Puffer hinzugefügt.

Routing

Es gibt zwei Arten von Routing im physischen Entwurfsprozess: globales Routing und detailliertes Routing. Globales Routing weist Routing-Ressourcen zu, die für Verbindungen verwendet werden. Es verfolgt auch die Zuordnung für ein bestimmtes Netz.

Detailliertes Routing übernimmt die eigentlichen Verbindungen. Verschiedene Einschränkungen, die während des Routings zu beachten sind, sind DRC, Drahtlänge, Timing usw.

Physische Überprüfung

Die physische Überprüfung überprüft die Richtigkeit des generierten Layoutdesigns. Dies beinhaltet die Überprüfung des Layouts

- Erfüllt alle technologischen Anforderungen - Design Rule Checking (DRC)

- Stimmt mit der ursprünglichen Netzliste überein - Layout vs. Schema (LVS)

- Hat keine Antenneneffekte - Überprüfung der Antennenregeln

- Dies beinhaltet auch die Überprüfung der Dichte auf der Ebene des gesamten Chips ... Die Reinigungsdichte ist ein sehr kritischer Schritt in den Knoten der unteren Technologie

- Erfüllt alle elektrischen Anforderungen - ERC (Electrical Rule Checking).

Layout-Nachbearbeitung

Die Layout-Nachbearbeitung, auch als Vorbereitung von Maskendaten bekannt , schließt häufig das physische Design und die Überprüfung ab. Es konvertiert das physikalische Layout (Polygone) in Maskendaten (Anweisungen für den Fotomaskenschreiber ). Es enthält

- Spanveredelung, wie das Einfügen von Firmen- / Chipetiketten und endgültigen Strukturen (z. B. Dichtungsring, Füllstrukturen),

- Generieren eines Fadenkreuzlayouts mit Testmustern und Ausrichtungsmarkierungen,

- Vorbereitung von Layout zu Maske, die Layoutdaten mit Grafikoperationen erweitert (z. B. Auflösungsverbesserungstechnologien , RET) und die Daten an Maskierungsproduktionsgeräte anpasst (Fotomaskenschreiber).