Delta-Sigma-Modulation - Delta-sigma modulation

| Passband - Modulation |

|---|

| Analoge Modulation |

| Digitale Modulation |

| Hierarchische Modulation |

| Breites Spektrum |

| Siehe auch |

Delta-Sigma ( ΔΣ ; oder Sigma-Delta , ΣΔ ) -Modulation ist ein Verfahren zum Codieren analoger Signale in digitale Signale, wie es in einem Analog-Digital-Wandler (ADC) gefunden wird. Es wird auch verwendet, um digitale Signale mit hoher Bitzahl und niedriger Frequenz in digitale Signale mit niedrigerer Bitzahl und höherer Frequenz umzuwandeln, als Teil des Prozesses zur Umwandlung digitaler Signale in analoge als Teil eines Digital-Analog-Wandlers (DAC .). ).

In einem herkömmlichen ADC wird ein Analogsignal wird abgetastet mit einer Abtastfrequenz und anschließend quantisiert , in einem Multi-Level - Quantisierer in ein digitales Signal . Dieser Prozess führt ein Quantisierungsfehlerrauschen ein. Der erste Schritt bei einer Delta-Sigma-Modulation ist die Delta-Modulation. Bei der Delta-Modulation wird die Änderung des Signals (sein Delta) codiert und nicht der Absolutwert. Das Ergebnis ist ein Strom von Pulsen, im Gegensatz zu einem Strom von Zahlen, wie es bei der Puls-Code-Modulation (PCM) der Fall ist . Bei der Delta-Sigma-Modulation wird die Genauigkeit der Modulation verbessert, indem der digitale Ausgang durch einen 1-Bit-DAC geleitet wird und das resultierende analoge Signal zum Eingangssignal (dem Signal vor der Delta-Modulation) addiert (Sigma) wird, wodurch der durch . eingeführte Fehler reduziert wird die Delta-Modulation.

Sowohl ADCs als auch DACs können Delta-Sigma-Modulation verwenden. Ein Delta-Sigma-ADC codiert zuerst ein analoges Signal unter Verwendung einer Hochfrequenz-Delta-Sigma-Modulation und wendet dann ein digitales Filter an, um einen digitalen Ausgang mit höherer Auflösung, aber niedrigerer Abtastfrequenz zu bilden. Ein Delta-Sigma-DAC codiert ein hochauflösendes digitales Eingangssignal in ein Signal mit niedrigerer Auflösung, aber höherer Abtastfrequenz, das auf Spannungen abgebildet und dann mit einem analogen Filter geglättet wird. In beiden Fällen vereinfacht die vorübergehende Verwendung eines Signals mit niedrigerer Auflösung das Schaltungsdesign und verbessert die Effizienz.

Vor allem wegen ihrer Kosteneffizienz und reduzierten Schaltungskomplexität hat diese Technik zunehmende Verwendung in modernen elektronischen Komponenten wie DACs, ADCs, Frequenzsynthesizern , Schaltnetzteilen und Motorsteuerungen gefunden . Der grob quantisierte Ausgang eines Delta-Sigma-Modulators wird gelegentlich direkt in der Signalverarbeitung oder als Darstellung zur Signalspeicherung verwendet. Beispielsweise speichert die Super Audio CD (SACD) die Ausgabe eines Delta-Sigma-Modulators direkt auf einer Platte.

Motivation

Die Delta-Sigma-Modulation wandelt ein analoges Spannungssignal in eine Pulsfrequenz oder Pulsdichte um, die als Pulsdichtemodulation (PDM) verstanden werden kann. Eine Folge von positiven und negativen Impulsen, die Bits mit einer bekannten festen Rate darstellen, ist sehr einfach zu erzeugen, zu übertragen und am Empfänger genau zu regenerieren, vorausgesetzt, dass nur das Timing und das Vorzeichen der Impulse wiederhergestellt werden können. Bei einer solchen Impulsfolge eines Delta-Sigma-Modulators kann die ursprüngliche Wellenform mit ausreichender Genauigkeit rekonstruiert werden. Im Gegensatz dazu würde ohne Umwandlung in einen Impulsstrom, sondern einfach nur das analoge Signal direkt übertragen, das gesamte Rauschen im System zum analogen Signal hinzugefügt, wodurch seine Qualität verringert würde. Die Verwendung von PDM als Signaldarstellung ist eine Alternative zur Puls-Code-Modulation (PCM), Abtasten und Quantisieren zu einem Multi-Bit-Code mit der Nyquist-Rate .

Analog-Digital-Wandlung

Beschreibung

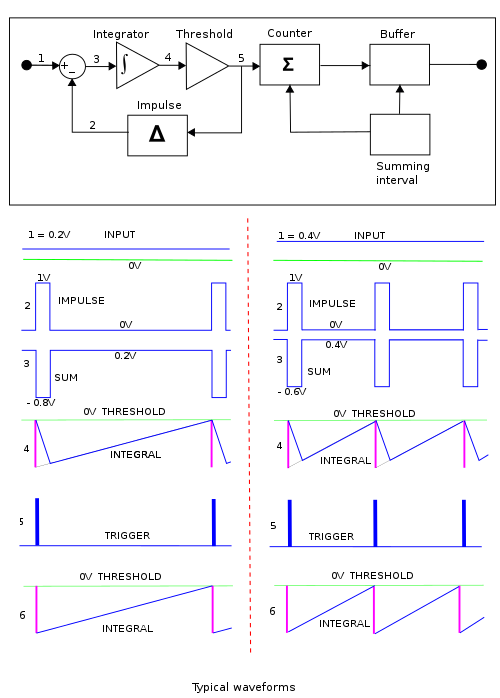

Ein Delta-Sigma- oder anderer Pulsdichte- oder Pulsfrequenzmodulator erzeugt einen Pulsstrom, in dem die Frequenz f der Pulse im Strom proportional zum analogen Spannungseingang v ist , so dass f = k · v , wobei k ist eine Konstante für die jeweilige Implementierung. Eine Rückkopplungsschleife überwacht das Integral von v und wenn dieses Integral um Δ inkrementiert wurde , was dadurch angezeigt wird, dass die Integralwellenform einen Schwellenwert T überschreitet, subtrahiert sie Δ vom Integral von v, so dass die kombinierte Wellenform zwischen T und T sägezahnt − Δ . Bei jedem Schritt wird dem Pulsstrom ein Puls hinzugefügt.

Ein Zähler summiert die Anzahl der Pulse, die in einer vorbestimmten Periode auftreten, so dass die Summe , , ist . In einer gegebenen Implementierung wird so gewählt, dass eine digitale Anzeige des Zählerstands eine Anzeige mit einem vorbestimmten Skalierungsfaktor ist. Da er jeden gewünschten Wert annehmen kann, kann er groß genug gemacht werden, um jede gewünschte Auflösung oder Genauigkeit zu ergeben.

Analyse

Zum Zwecke der Einführung veranschaulicht 1 das Konzept der Spannungs-Frequenz-Umwandlung in einer ungetakteten Form, die der Delta-Sigma-Modulation ähnelt und als asynchrone Modulation , asynchrone Delta-Sigma-Modulation oder freilaufende Modulatoren bezeichnet wird .

Darunter sind Wellenformen an den mit den Nummern 1 bis 5 bezeichneten Punkten für einen Eingang von 0,2 Volt in der linken Spalte und 0,4 Volt in der rechten Spalte dargestellt. Der Strom von Delta-Impulsen, der bei jeder Schwellenüberschreitung erzeugt wird, ist bei (2) gezeigt und die Differenz zwischen (1) und (2) ist bei (3) gezeigt. Diese Differenz wird integriert , um die Wellenform (4) zu erzeugen. Der Schwellenwertdetektor erzeugt einen Impuls (5), der beginnt, wenn die Wellenform (4) den Schwellenwert überschreitet, und gehalten wird, bis die Wellenform (4) unter den Schwellenwert fällt. Die Schwelle (5) veranlasst den Impulsgenerator, einen Impuls fester Stärke zu erzeugen.

Das Integral (4) überschreitet in der rechten Spalte die Schwelle in der Hälfte der Zeit als in der linken Spalte. Dadurch wird die Impulsfrequenz verdoppelt. Daher erhöht sich die Zählung mit der doppelten Geschwindigkeit rechts zu der links; diese Pulsratenverdopplung stimmt mit der Verdoppelung der Eingangsspannung überein.

Die Konstruktion der bei (4) veranschaulichten Wellenformen wird durch Konzepte unterstützt, die mit der Dirac-Deltafunktion verbunden sind , da definitionsgemäß alle Impulse der gleichen Stärke bei der Integration den gleichen Schritt erzeugen. Dann wird (4) unter Verwendung eines Zwischenschritts (6) konstruiert, eine hypothetische Wellenform nicht in der Schaltung, sondern in der jeder integrierte ideale Deltafunktionsimpuls zu einem Schritt integriert wird. Die Wirkung der endlichen Dauer des tatsächlichen Impulses wird in (4) konstruiert, indem eine Linie von der Basis des Impulsschritts bei null Volt gezogen wird, um die Abklinglinie von (6) bei der vollen Dauer des Impulses zu schneiden.

In der Schaltung außerhalb der Schleife ist das Summierintervall eine vorbestimmte feste Zeit, und bei seinem Ablauf wird der Zählerstand gespeichert und der Puffer und der Zähler werden zurückgesetzt. Der Puffer präsentiert dann eine Folge von digitalen Werten, die Quantisierungen der analogen Signalpegel während der Summierungsintervalle entsprechen. Die Verwendung eines Summierintervalls ist ein Weg (nicht unbedingt der ideale Weg), um den asynchronen Impulsstrom zu einem Code zu quantisieren; es wird weniger Quantisierungsfehler aufweisen, wenn der Intervallstart mit einem Impuls synchronisiert ist.

Delta-Sigma-Wandler schränken den Betrieb des Impulsgenerators weiter so ein, dass der Start des Impulses bis zum nächsten Auftreten der geeigneten Taktimpulsgrenze verzögert wird. Die Wirkung dieser Verzögerung ist in Fig. 1a für eine Folge von Impulsen dargestellt, die in nominellen 2,5 Taktintervallen auftreten.

Praktische Anwendung

Ein Schaltplan für eine Implementierung eines Delta-Sigma-Modulators ist in 1b gezeigt, mit den zugehörigen Wellenformen in 1c . Die in Abbildung 1c gezeigten Wellenformen sind ungewöhnlich kompliziert, da sie das Schleifenverhalten unter extremen Bedingungen veranschaulichen sollen, V in gesättigt bei voller Skala von 1,0 V und gesättigt bei Null. Ein Zwischenzustand wird ebenfalls angezeigt, V in bei 0,4 V , wo er dem Betrieb der Illustration von Abbildung 1 sehr ähnlich ist.

Von oben in Abbildung 1c sind die Wellenformen, die wie im Schaltplan bezeichnet sind, wie folgt:

- Die Uhr

- (a) V in – dies wird als Variieren von anfangs 0,4 V bis 1,0 V und dann bis Null Volt angezeigt, um die Auswirkung auf die Rückkopplungsschleife zu zeigen.

- (b) Die Impulswellenform, die den Integrator speist. Gesteuert durch Flip-Flop- Ausgang (f) unten.

- (c) Der Strom in den Kondensator, I c , ist die lineare Summe der Stoßreferenzspannung geteilt durch R und V in geteilt durch R . Um diese Summe als Spannung darzustellen, wird das Produkt R × I c aufgetragen. Die Eingangsimpedanz des Verstärkers wird als so hoch angesehen, dass die Stromaufnahme am Eingang vernachlässigt wird. Der Kondensator ist zwischen den negativen Eingangsanschluss des Verstärkers und seinen Ausgangsanschluss geschaltet. Mit dieser Verbindung bietet es einen negativen Rückkopplungspfad um den Verstärker herum. Die Eingangsspannungsänderung ist gleich der Ausgangsspannungsänderung geteilt durch die Verstärkerverstärkung. Bei sehr hoher Verstärkerverstärkung kann die Änderung der Eingangsspannung vernachlässigt werden und so wird die Eingangsspannung nahe der Spannung am positiven Eingangsanschluss gehalten, die in diesem Fall auf 0 V gehalten wird. Da die Spannung am Eingangsanschluss 0 V beträgt, beträgt die Spannung an R einfach V in, so dass der Strom in den Kondensator die Eingangsspannung geteilt durch den Widerstand von R ist .

- (d) Das negierte Integral von I c . Diese Negation ist Standard für den Operationsverstärker-Integrator und kommt zustande, weil der Strom in den Kondensator am Verstärkereingang der Strom aus dem Kondensator am Verstärkerausgang ist und die Spannung das Integral des Stroms geteilt durch die Kapazität C ist .

- (e) Der Komparatorausgang. Der Komparator ist ein Verstärker mit sehr hoher Verstärkung, dessen Plus-Eingangsanschluss mit Bezug auf 0,0 V verbunden ist. Immer wenn der negative Eingangsanschluss in Bezug auf den positiven Anschluss des Verstärkers negativ wird, sättigt der Ausgang die positive und umgekehrt die negative Sättigung für den positiven Eingang. Somit wird der Ausgang positiv gesättigt, wenn das Integral (d) unter den 0-V-Referenzpegel fällt, und der Ausgang bleibt dort, bis (d) in Bezug auf den 0-V-Referenzwert positiv wird.

- (f) Der Impulszeitgeber ist ein positiv flankengetriggertes Flip-Flop vom D-Typ . Die an D angelegte Eingangsinformation wird beim Auftreten der positiven Flanke des Taktimpulses an Q übertragen. Wenn also der Komparatorausgang (e) positiv ist, wird Q positiv oder bleibt positiv bei der nächsten positiven Taktflanke. Wenn (e) negativ ist, wird Q bei der nächsten positiven Taktflanke negativ. Q steuert den elektronischen Schalter, um den Stromimpuls (b) in den Integrator zu erzeugen. Prüfung der Wellenform (e) während der Anfangsperiode veranschaulicht, wenn V in 0,4 V beträgt, zeigt (e) die Schwelle weit vor der positiven Flanke des Taktimpulses kreuzt , so daß eine nennenswerte Verzögerung , bevor der Impuls beginnt , ist. Nach dem Start des Impulses gibt es eine weitere Verzögerung, während (d) über die Schwelle zurücksteigt. Während dieser Zeit bleibt der Komparatorausgang (e) hoch, wird aber vor der nächsten Triggerflanke niedrig, woraufhin der Impulstimer niedrig wird, um dem Komparator zu folgen. Somit bestimmt die Uhr teilweise die Dauer des Impulses. Beim nächsten Impuls wird die Schwelle unmittelbar vor der Triggerflanke überschritten, der Komparator ist also nur kurz positiv. V in (a) geht dann kurz vor dem Ende des nächsten Impulses auf den Skalenendwert + V ref . Für den Rest dieses Impulses geht der Kondensatorstrom (c) auf Null und daher geht die Integratorsteigung kurz auf Null. Nach diesem Impuls fließt der volle positive Strom (c) und der Integrator sinkt mit seiner maximalen Geschwindigkeit und überschreitet so den Schwellenwert lange vor der nächsten Triggerflanke. An dieser Flanke beginnt der Impuls und der Strom V in wird nun mit dem Referenzstrom abgeglichen, so dass der Nettokondensatorstrom (c) Null ist. Die Integration hat jetzt eine Steigung von Null und bleibt auf dem negativen Wert, den sie zu Beginn des Impulses hatte. Dies hat zur Folge, dass der Impulsstrom eingeschaltet bleibt, weil Q positiv hängen bleibt, weil der Komparator bei jeder Triggerflanke positiv hängt. Dies steht im Einklang mit aneinandergrenzenden, aneinanderstoßenden Impulsen, die für eine Eingabe in vollem Umfang repräsentativ sind. Als nächstes geht V in (a) auf Null, was bewirkt, dass die Stromsumme (c) vollständig negativ wird und das Integral ansteigt. Er überschreitet kurz darauf die Schwelle und dieser wiederum folgt Q, wodurch der Stoßstrom abgeschaltet wird. Der Kondensatorstrom (c) ist jetzt null und somit ist die Integralsteigung null und bleibt konstant auf dem Wert, den er am Ende des Impulses erreicht hatte.

- (g) Der Zählstrom wird durch Gating des negierten Takts mit Q erzeugt, um diese Wellenform zu erzeugen. Danach werden das Summierintervall, die Sigma-Zählung und die gepufferte Zählung unter Verwendung geeigneter Zähler und Register erzeugt.

Verbesserungen bei Auflösung und Rauschen

Eine Untersuchung von Fig. 1c(g) zeigt, dass es Nullimpulse im Zählstrom gibt, wenn die Eingangsspannung Null ist. Dieser Zustand kann dazu führen, dass hochfrequente Anteile eines komplexen Signals nicht aufgelöst werden. Dieser Effekt wird als Intermodulationsverzerrung (IMD) bezeichnet. Eine der Fallstricke bei der Anwendung der linearen Analyse auf ein nichtlineares System besteht darin, dass IMD, da es eine Folge von Nichtlinearität sein kann, in der Analyse nicht vorhanden ist. Rein zu Veranschaulichungszwecken wäre ein Verfahren, dies zu mildern, das Hinzufügen einer konstanten Vorspannung von 0,5 Volt zu der Eingangsspannung, so dass sie jetzt +/– 0,5 V um die Vorspannung schwingen kann. Dieser hat jetzt Nullimpulse im Countstream, wenn der Eingang -0,5 V beträgt. Dann müssen wir den Eingangshub auf etwa +/- 0,4 V begrenzen, damit die minimale Zählstromfrequenz größer als Null ist. Wir können die Taktfrequenz so wählen, dass die minimale Zählstromfrequenz bei −0,4 V viel größer als die Nyquist-Rate ist , sodass selbst die höchste Eingangsfrequenzkomponente aufgelöst wird. Wir können die Taktfrequenz noch höher erhöhen, bis ein Tiefpassfilter die Pulsationen ausreichend entfernt, während das Eingangssignal vollständig wiederhergestellt wird. In dieser erläuternden Diskussion stellt das gefilterte Signal auch die Vorspannung wieder her, die durch einen analogen Addierer entfernt werden kann, während die Gleichstromkomponente des Eingangssignals noch erhalten bleibt.

Bemerkungen

Laut Wooley stammt die bahnbrechende Arbeit, die Feedback mit Oversampling kombiniert, um eine Delta-Modulation zu erreichen, von F. de Jager im Jahr 1952.

Die Delta-Sigma-Konfiguration wurde von Inose et al. 1962, um Probleme bei der genauen Übertragung analoger Signale zu lösen. In dieser Anwendung wurde der Impulsstrom übertragen und das ursprüngliche analoge Signal mit einem Tiefpassfilter wiederhergestellt, nachdem die empfangenen Impulse reformiert worden waren. Dieses Tiefpassfilter führte die mit verbundene Summationsfunktion durch. Die hochmathematische Behandlung von Übertragungsfehlern wurde von ihnen eingeführt und ist geeignet, wenn sie auf den Pulsstrom angewendet wird, aber diese Fehler gehen bei dem mit verbundenen Akkumulationsvorgang verloren.

Für die Analog-Digital-Umwandlungsanwendung ist jeder Impuls im Zählstrom ein Abtastwert des Mittelwerts der Eingangsspannung gleich der Referenzspannung geteilt durch das Intervall zwischen den Impulsen, ts. Dies, weil es sich um eine Integration der Eingangswellenform über das Intervall ts handelt. Die Frequenzbereichsanalyse der komplexen Wellenform in diesem Intervall ts wird sie durch die Summe einer Konstanten plus einer Grundwelle und Harmonischen darstellen, von denen jede eine exakte ganzzahlige Anzahl von Zyklen über ts aufweist. Das Integral einer Sinuswelle über einen oder mehrere volle Zyklen ist Null. Daher verringert sich das Integral der eingehenden Wellenform über das Intervall ts auf den Mittelwert über das Intervall. Der während des Summierungsintervalls akkumulierte Zählwert N stellt N Abtastwerte des Mittelwerts dar, und N geteilt durch den das Summierungsintervall definierenden Zählwert ist somit der Mittelwert des Mittelwerts und unterliegt somit einer geringen Varianz.

Digital-Analog-Wandlung

Im Allgemeinen wandelt ein DAC eine digitale Zahl N, die einen analogen Wert darstellt, in diesen analogen Spannungswert um. Um die Umwandlung durchzuführen, wird die digitale Zahl zuerst in einen Zähler geladen. Dann wird der Zähler mit einer Reihe von Impulsen, die in der Anzahl N gleich sind, auf Null heruntergezählt. Jeder Impuls der Reihe erhält ein bekanntes Integral . Dann wird der String integriert, um N.δ zu erzeugen, die Summe der Impulse. Dies ist die erforderliche Analogspannung.

Bei einigen Anwendungen, bei denen ein analoges Signal durch eine Reihe digitaler Zahlen dargestellt wird, die eine Umwandlung in einen frequenzmodulierten Strom erfordern, kann es ausreichend sein, den Impulsstrom (zwei oder drei Ebenen) zu verwenden, der sich aus der DAC-Umwandlung jeder Zahl N ergibt und wenden Sie diesen Stream durch einen Tiefpassfilter direkt auf den Ausgang an. Die Ausgabe vor dem Filtern wird ein grob frequenzmodulierter Strom mit Impulsbündeln sein, die in Länge und Anzahl proportional zum Analogon von N sind, getrennt durch Leerintervalle zwischen den Bündeln.

Um die Leerintervalle zu entfernen und die Rauschleistung zu verbessern, kann die vollständige Umwandlung jedes aufeinanderfolgenden N in eine analoge Spannung durch den oben beschriebenen DAC in einer Abtast- und Halteschaltung gehalten und dann an einen Delta-Sigma-Wandler weitergeleitet werden, um einen Strom von zusammenhängenden Bursts zu erzeugen von denen jede ihre Frequenz proportional zu ihrem erzeugenden N hat.

Dezimierungsstrukturen

Die konzeptionell einfachste Dezimierungsstruktur ist ein Zähler, der zu Beginn jeder Integrationsperiode auf Null zurückgesetzt und dann am Ende der Integrationsperiode ausgelesen wird.

Die mehrstufige Noise-Shaping-(MASH)-Struktur hat eine Noise-Shaping- Eigenschaft und wird üblicherweise in digitalen Audio- und Fractional-N-Frequenz-Synthesizern verwendet. Es umfasst zwei oder mehr kaskadierte überlaufende Akkumulatoren, von denen jeder einem Sigma-Delta-Modulator erster Ordnung entspricht. Die Übertragsausgaben werden durch Summationen und Verzögerungen kombiniert, um eine binäre Ausgabe zu erzeugen, deren Breite von der Anzahl der Stufen (Reihenfolge) des MASH abhängt. Neben seiner Noise-Shaping-Funktion hat es zwei weitere attraktive Eigenschaften:

- einfach in Hardware zu implementieren; es werden nur gängige digitale Blöcke wie Akkumulatoren , Addierer und D-Flip-Flops benötigt

- bedingungslos stabil (es gibt keine Rückkopplungsschleifen außerhalb der Akkumulatoren)

Eine sehr beliebte Dezimierungsstruktur ist der Sinc- Filter. Für Modulatoren zweiter Ordnung liegt der sinc3- Filter nahe am Optimum.

Beispiel für Dezimierung

Bei einem 8:1-Dezimationsfilter und einem 1-Bit-Bitstream:

- die Samplefrequenz wird um den Faktor acht reduziert

- der serielle (1-Bit) Eingangsbus wird ein paralleler (3-Bit) Ausgangsbus.

Zum Beispiel enthält der Eingabestrom 10010110 4 1s. Das Dezimierungsergebnis ist 4/8 = 0,5. Dieses Ergebnis lässt sich durch die 3-Bit-Binärzahl 100 darstellen, die der Hälfte der größtmöglichen Zahl entspricht. Sobald die Dezimierung angewendet wird und die n Bitcodes übertragen werden, wird das Signal zu einer Pulscodemodulation . Die Dezimierung ist stark mit der Delta-Sigma-Modulation verbunden, ist jedoch unterschiedlich.

Variationen

Es gibt viele Arten von ADC, die diese Delta-Sigma-Struktur verwenden. Die obige Analyse konzentriert sich auf den einfachsten Sigma-Delta-ADC mit gleichförmiger Dezimation auf 2 Ebenen erster Ordnung. Viele ADCs verwenden eine 5-Level-sinc3-Sigma-Delta-Struktur zweiter Ordnung. Vieles von dem, was folgt, verwendet eine geheimnisvolle Kurzschrift, die Symbole verwendet, die Betriebsfunktionen darstellen, wobei die Analyse in Form von Laplace-Transformationen usw. gegeben ist. Dies ist die Lingua Franca der Datenübertragungsindustrie und wird nicht an die Öffentlichkeit kommuniziert. Wenn eine umfassendere Dokumentation einer bestimmten Methode erforderlich ist, suchen Sie nicht weiter als die Patente. (Patentprüfer verlangen im Allgemeinen eine vollständige Offenlegung.) Eine ausgezeichnete Geschichte ist "The Evolution of Oversampling Analog-to-Digital Converters" von Bruce A. Wooley, die viele Verweise auf die relevanten Patente enthält.

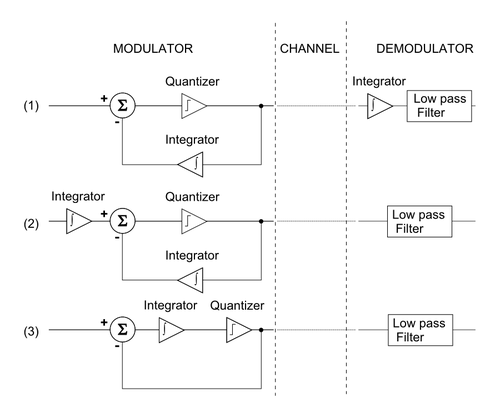

Modulator zweiter und höherer Ordnung

Die Anzahl der Integratoren und folglich die Anzahl der Rückkopplungsschleifen gibt die Ordnung eines -Modulators an; ein ΔΣ-Modulator zweiter Ordnung ist in Abbildung 4 gezeigt. Modulatoren erster Ordnung sind bedingungslos stabil, aber für Modulatoren höherer Ordnung muss eine Stabilitätsanalyse durchgeführt werden.

3-stufiger und höherer Quantisierer

Der Modulator kann auch nach der Anzahl der Bits klassifiziert werden, die er in seiner Ausgabe hat, die streng von der Ausgabe des Quantisierers abhängt. Der Quantisierer kann mit einem N-Level- Komparator realisiert werden, daher hat der Modulator einen log 2 N- Bit-Ausgang. Ein einfacher Komparator hat 2 Pegel, ebenso wie der 1-Bit-Quantisierer; ein 3-Level-Quantisierer wird als "1,5"-Bit-Quantisierer bezeichnet; ein 4-Level-Quantisierer ist ein 2-Bit-Quantisierer; ein 5-Stufen-Quantisierer wird als "2,5-Bit"-Quantisierer bezeichnet.

Beziehung zur Delta-Modulation

Delta-Sigma - Modulation durch inspiriert Delta - Modulation , wie in Abbildung 2 gezeigt , wenn die Quantisierung war homogen (zB wenn es linear ), wird die folgende würde eine ausreichende Ableitung der Äquivalenz liegen:

- Beginnen Sie mit einem Blockschaltbild eines Delta-Modulators/Demodulators.

- Die Linearitätseigenschaft der Integration, , ermöglicht es, den Integrator, der das analoge Signal im Demodulatorabschnitt rekonstruiert, vor den Delta-Modulator zu bewegen.

- Auch hier ermöglicht die Linearitätseigenschaft der Integration die Kombination der beiden Integratoren und ein Delta-Sigma-Modulator/Demodulator-Blockdiagramm wird erhalten.

Da der Quantisierer nicht homogen ist, wird Delta-Sigma von der Delta-Modulation inspiriert , aber die beiden sind im Betrieb unterschiedlich.

Aus dem ersten Blockschaltbild in Bild 2 kann der Integrator im Rückkopplungspfad entfernt werden, wenn die Rückkopplung direkt vom Eingang des Tiefpassfilters genommen wird. Daher sieht der Tiefpassfilter für die Delta-Modulation des Eingangssignals u das Signal

Die Sigma-Delta-Modulation des gleichen Eingangssignals platziert jedoch am Tiefpassfilter

Mit anderen Worten vertauschen Delta-Sigma und Delta-Modulation die Position des Integrators und des Quantisierers. Der Nettoeffekt ist eine einfachere Implementierung, die den zusätzlichen Vorteil hat, dass das Quantisierungsrauschen weg von interessierenden Signalen geformt wird (dh interessierende Signale werden tiefpassgefiltert, während das Quantisierungsrauschen hochpassgefiltert wird). Dieser Effekt wird mit zunehmendem Oversampling dramatischer , wodurch das Quantisierungsrauschen einigermaßen programmierbar ist. Andererseits formt Delta-Modulation sowohl Rauschen als auch Signal gleichermaßen.

Zusätzlich kann der Quantisierer (zB Komparator ) verwendet , in Delta - Modulation hat einen kleinen Ausgang einen kleinen Schritt nach oben und unten der quantisierte Näherung des Eingangs während der Quantisierer in Delta-Sigma verwendet darstellen müssen Werte annehmen außerhalb des Bereichs des Eingangssignals, wie in Abbildung 3 gezeigt.

Im Allgemeinen hat Delta-Sigma einige Vorteile gegenüber der Delta-Modulation:

- Die Struktur ist vereinfacht als

- es wird nur ein Integrator benötigt,

- der Demodulator kann ein einfacher linearer Filter (zB RC- oder LC-Filter) sein, um das Signal zu rekonstruieren und

- der Quantisierer (zB Komparator) kann Vollausgänge haben

- Der quantisierte Wert ist das Integral des Differenzsignals, wodurch es weniger empfindlich auf die Änderungsrate des Signals reagiert.

Formeln der Quantisierungstheorie

Wenn ein Signal quantisiert wird, weist das resultierende Signal ungefähr die Statistik zweiter Ordnung eines Signals mit hinzugefügtem unabhängigen weißen Rauschen auf. Unter der Annahme, dass der Signalwert im Bereich einer Stufe des quantisierten Wertes mit gleicher Verteilung liegt, ist der Effektivwert dieses Quantisierungsrauschens

In Wirklichkeit ist das Quantisierungsrauschen natürlich nicht unabhängig vom Signal und diese Abhängigkeit führt zu Grenzzyklen und ist die Quelle von Leerlauftönen und Musterrauschen in Sigma-Delta-Wandlern.

Das Quantisierungsrauschen kann durch Erhöhen des Oversampling-Verhältnisses (OSR), definiert durch ., reduziert werden

wobei die Abtastfrequenz und die Nyquist-Rate ist .

Die RMS- Rauschspannung innerhalb des interessierenden Bandes ( ) kann als OSR . ausgedrückt werden

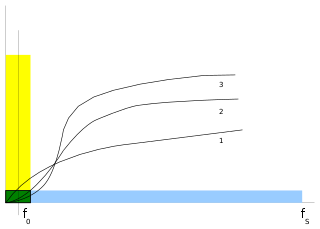

Oversampling

ΔΣ-Modulation ist eine Technik der Überabtastung , um das Rauschen im interessierenden Band (grün in Abbildung 5) zu reduzieren, wodurch die Verwendung hochpräziser analoger Schaltungen für das Anti-Aliasing-Filter vermieden wird . Das gesamte Quantisierungsrauschen ist sowohl bei einem Nyquist-Wandler (in gelb) als auch bei einem Oversampling-Wandler (in blau) gleich, verteilt sich jedoch über ein anderes Spektrum. In ΔΣ-Wandlern wird das Rauschen bei niedrigen Frequenzen, dem Band, in dem sich das interessierende Signal befindet, weiter reduziert und bei den höheren Frequenzen erhöht, wo es herausgefiltert werden kann. Diese Technik wird als Rauschformung bezeichnet.

Bei einem Delta-Sigma-Modulator erster Ordnung wird das Rauschen durch ein Filter mit der Übertragungsfunktion H n ( z ) = [1 − z −1 ] geformt . Unter der Annahme, dass die Abtastfrequenz f s im Vergleich zu einer interessierenden Signalfrequenz f 0 groß ist , kann das Quantisierungsrauschen in der gewünschten Signalbandbreite wie folgt angenähert werden:

- .

Ähnlich wird bei einem Delta-Sigma-Modulator zweiter Ordnung das Rauschen durch ein Filter mit der Übertragungsfunktion H n ( z ) = [1 − z −1 ] 2 geformt . Das Inband-Quantisierungsrauschen kann wie folgt angenähert werden:

- .

Im Allgemeinen beträgt die Varianz des Quantisierungsrauschens im Band für einen -Modulator N- ter Ordnung:

- .

Wenn die Abtastfrequenz verdoppelt wird, wird das Signal-Quantisierungs-Rausch-Verhältnis um 6 N + 3 dB für einen -Modulator N- ter Ordnung verbessert. Je höher das Oversampling-Verhältnis, desto höher das Signal-Rausch-Verhältnis und desto höher die Auflösung in Bit.

Ein weiterer wichtiger Aspekt, der durch Oversampling gegeben ist, ist der Kompromiss zwischen Geschwindigkeit und Auflösung. Der dem Modulator nachgeschaltete Dezimationsfilter filtert nicht nur das gesamte abgetastete Signal im interessierenden Band (beseitigt das Rauschen bei höheren Frequenzen), sondern reduziert auch die Frequenz des Signals, wodurch seine Auflösung erhöht wird. Dies wird durch eine Art Mittelung des Bitstroms mit höherer Datenrate erreicht.

Benennung

Die Technik wurde erstmals Anfang der 1960er Jahre von Professor Yasuhiko Yasuda während seines Studiums an der Universität Tokio vorgestellt . Der Name Delta-Sigma kommt direkt von der Anwesenheit eines Delta-Modulators und eines Integrators, wie zuerst von Inose et al. eingeführt. in ihrer Patentanmeldung. Das heißt, der Name kommt vom Integrieren oder Summieren von Differenzen , die in der Mathematik Operationen sind, die normalerweise mit den griechischen Buchstaben Sigma bzw. Delta verbunden sind. Beide Namen Sigma-Delta und Delta-Sigma werden häufig verwendet.

Siehe auch

Verweise

Weiterlesen

- Walt Kester (Oktober 2008). "ADC-Architekturen III: Sigma-Delta-ADC-Grundlagen" (PDF) . Analoge Geräte . Abgerufen 2010-11-02 .

- R. Jacob Baker (2009). CMOS-Mixed-Signal-Schaltungsdesign (2. Aufl.). Wiley-IEEE. ISBN 978-0-470-29026-2.

- R. Schreier; G. Temes (2005). Delta-Sigma-Datenkonverter verstehen . ISBN 978-0-471-46585-0.

- S. Norsworthy; R. Schreier; G. Temes (1997). Delta-Sigma-Datenkonverter . ISBN 978-0-7803-1045-2.

- J. Süßigkeiten; G. Temes (1992). Oversampling-Delta-Sigma-Datenkonverter . ISBN 978-0-87942-285-1.

Externe Links

- 1-Bit-A/D- und D/A-Wandler

- Sigma-Delta-Techniken erweitern die DAC-Auflösung Artikel von Tim Wescott 2004-06-23

- Tutorial zum Entwerfen von Delta-Sigma-Modulatoren: Teil I und Teil II von Mingliang (Michael) Liu

- Gabor Temes' Veröffentlichungen

- Sigma-Delta Modulation Primer Teil II Enthält Blockdiagramme, Code und einfache Erklärungen

- Simulink-Beispielmodell und Skripte für zeitkontinuierliches Sigma-Delta-ADC Enthält Beispiel-Matlab-Code und Simulink-Modell

- Bruce Wooleys Delta-Sigma-Konverter-Projekte

- Eine Einführung in Delta-Sigma-Wandler (die sowohl ADCs als auch DACs Sigma-Delta abdeckt)

- Entmystifizierung von Sigma-Delta-ADCs . Dieser ausführliche Artikel behandelt die Theorie hinter einem Delta-Sigma-Analog-Digital-Wandler.

- Ein-Bit-Delta-Sigma-D/A-Umwandlung Teil I: Theorieartikel von Randy Yates, vorgestellt auf der comp.dsp-Konferenz 2004

- MASH-Struktur (Multi-Stage Noise SHaping) mit Theorie und einer Block-Level-Implementierung eines MASH

- Zeitkontinuierliche Sigma-Delta-ADC-Rauschformungsfilter-Schaltungsarchitekturen diskutiert architektonische Kompromisse für zeitkontinuierliche Sigma-Delta-Rauschformungsfilter

- Delta-Sigma-Wandler: Modulation – intuitive Motivation, warum ein Delta-Sigma-Modulator funktioniert

- Digitaler Beschleunigungsmesser mit Rückkopplungssteuerung mit Sigma-Delta-Modulation