Wafer (Elektronik) - Wafer (electronics)

|

||

|

In Elektronik , ein Wafer (auch genannt Scheibe oder Substrat ) ist eine dünne Scheibe Halbleiter , wie beispielsweise ein kristallines Silizium (c-Si), für die verwendete Herstellung von integrierten Schaltkreisen und in der Photovoltaik , in der Herstellung von Solarzellen . Der Wafer dient als Substrat für in und auf dem Wafer eingebaute mikroelektronische Bauelemente. Es durchläuft viele Mikrofabrikationsprozesse wie Dotierung , Ionenimplantation , Ätzen , Dünnschichtabscheidung verschiedener Materialien und photolithografische Strukturierung. Schließlich werden die einzelnen Mikroschaltungen durch Wafer-Würfeln getrennt und als integrierte Schaltung verpackt .

Geschichte

In den 1950er Jahren, Mohamed Atalla untersucht , die Oberflächeneigenschaften von Silizium - Halbleitern bei Bell Labs , wo er eine neue Methode der angenommenen Halbleitervorrichtungsherstellung , Beschichten eines Siliciumwafers mit einer isolierenden Schicht aus Siliziumoxid , so daß die Elektrizität zuverlässig in den leitenden Silizium eindringen konnte unten Überwindung der Oberflächenzustände, die verhinderten, dass Elektrizität die Halbleiterschicht erreichte. Dies ist als Oberflächenpassivierung bekannt , eine Methode, die später für die Halbleiterindustrie kritisch wurde, da sie die Massenproduktion von integrierten Siliziumschaltungen (ICs) ermöglichte. Die Oberflächenpassivierungsmethode wurde 1957 von Atalla vorgestellt und war später die Grundlage für das 1959 von Atalla und Dawon Kahng erfundene Metalloxid-Halbleiter (MOS) -Verfahren .

Bis 1960 wurden Siliziumwafer in den USA von Unternehmen wie MEMC / SunEdison hergestellt . 1965 meldeten die amerikanischen Ingenieure Eric O. Ernst, Donald J. Hurd und Gerard Seeley unter IBM das Patent US3423629A für das erste Epitaxiegerät mit hoher Kapazität an.

Formation

Wafer bestehen aus hochreinem, nahezu fehlerfreiem einkristallinem Material mit einer Reinheit von 99,9999999% ( 9 N ) oder höher. Ein Verfahren zur Bildung kristalliner Wafer ist das vom polnischen Chemiker Jan Czochralski erfundene Czochralski-Wachstum . Bei diesem Verfahren wird ein zylindrischer Block aus hochreinem monokristallinem Halbleiter wie Silizium oder Germanium , genannt Boule , gebildet, indem ein Impfkristall aus einer Schmelze gezogen wird . Donorverunreinigungsatome wie Bor oder Phosphor im Fall von Silizium können dem geschmolzenen intrinsischen Material in genauen Mengen zugesetzt werden, um den Kristall zu dotieren , wodurch er in einen extrinsischen Halbleiter vom n-Typ oder p-Typ umgewandelt wird .

Die Kugel wird dann mit einer Wafersäge (einer Art Drahtsäge ) in Scheiben geschnitten und poliert , um Wafer zu bilden. Die Größe der Wafer für die Photovoltaik beträgt 100–200 mm² und die Dicke 100–500 μm. In der Elektronik werden Wafergrößen von 100 bis 450 mm Durchmesser verwendet. Die größten hergestellten Wafer haben einen Durchmesser von 450 mm, werden aber noch nicht allgemein verwendet.

Reinigen, Texturieren und Ätzen

Wafer werden mit schwachen Säuren gereinigt , um unerwünschte Partikel zu entfernen oder Schäden zu reparieren, die während des Sägevorgangs verursacht wurden. Es gibt verschiedene Standardreinigungsverfahren, um sicherzustellen, dass die Oberfläche eines Siliziumwafers keine Verunreinigungen enthält. Eine der effektivsten Methoden ist RCA Clean . Bei Verwendung für Solarzellen werden die Wafer so strukturiert, dass eine raue Oberfläche entsteht, um ihre Effizienz zu erhöhen. Das erzeugte PSG ( Phosphosilikatglas ) wird beim Ätzen vom Rand des Wafers entfernt .

Wafereigenschaften

Standard-Wafergrößen

Semicon

Siliziumwafer sind in verschiedenen Durchmessern von 25,4 mm (1 Zoll) bis 300 mm (11,8 Zoll) erhältlich. Halbleiterfertigungsanlagen , umgangssprachlich als Fabs bekannt , werden durch den Durchmesser der Wafer definiert, für deren Herstellung sie bearbeitet werden. Der Durchmesser wurde schrittweise vergrößert, um den Durchsatz zu verbessern und die Kosten mit der aktuellen Fabrik auf dem neuesten Stand der Technik unter Verwendung von 300 mm zu senken , wobei 450 mm vorgeschlagen wurden . Intel , TSMC und Samsung separat forschen auf das Aufkommen von 450 mm „ Prototyp “ (Forschung) Fabs , obwohl ernsthafte Hürden bleiben.

| Wafergröße | Typische Dicke | Jahr Prodn | Gewicht pro Wafer | 100 mm2 (10 mm) Chip pro Wafer |

|---|---|---|---|---|

| 25 mm (1 Zoll) | 1960 | |||

| 51 mm (2 Zoll) | 275 μm | 1969 | ||

| 76 mm (3 Zoll) | 375 μm | 1972 | ||

| 100 mm (4 Zoll) | 525 μm | 1976 | 10 Gramm | 56 |

| 125 mm (4,9 Zoll) | 625 μm | 1981 | ||

| 150 mm (5,9 Zoll, üblicherweise als "6 Zoll" bezeichnet) | 675 μm | 1983 | ||

| 200 mm (7,9 Zoll, üblicherweise als "8 Zoll" bezeichnet) | 725 μm. | 1992 | 53 Gramm | 269 |

| 300 mm (11,8 Zoll, üblicherweise als "12 Zoll" bezeichnet) | 775 μm | 2002 | 125 Gramm | 640 |

| 450 mm (17,7 Zoll) (vorgeschlagen). | 925 μm | Zukunft | 342 Gramm | 1490 |

| 675 Millimeter (26,6 Zoll) (theoretisch). | Unbekannt. | Zukunft |

Wafer, die unter Verwendung anderer Materialien als Silizium gezüchtet wurden, haben andere Dicken als ein Siliziumwafer mit demselben Durchmesser. Die Waferdicke wird durch die mechanische Festigkeit des verwendeten Materials bestimmt; Der Wafer muss dick genug sein, um sein eigenes Gewicht zu tragen, ohne während der Handhabung Risse zu bekommen. Die tabellarischen Dicken beziehen sich auf den Zeitpunkt der Einführung dieses Prozesses und sind derzeit nicht unbedingt korrekt. Beispielsweise ist der IBM BiCMOS7WL-Prozess auf 8 in Wafern eingestellt, diese sind jedoch nur 200 μm dick. Das Gewicht des Wafers steigt zusammen mit seiner Dicke und seinem Durchmesser.

Historische Zunahme der Wafergröße

Ein Einheitswafer- Herstellungsschritt , wie beispielsweise ein Ätzschritt, kann mehr Chips erzeugen, die proportional zur Zunahme der Waferfläche sind, während die Kosten des Einheitsherstellungsschritts langsamer steigen als die Waferfläche. Dies war die Kostenbasis für die Erhöhung der Wafergröße. Die Umstellung von 200-mm-Wafern auf 300-mm-Wafer begann im Jahr 2000 und reduzierte den Preis pro Chip um etwa 30-40%. Wafer mit größerem Durchmesser ermöglichen mehr Chips pro Wafer.

Photovoltaik

Die Wafergröße M1 (156,75 mm) wird in China ab 2020 auslaufen. Eine Reihe von nicht standardmäßigen Größen ist entstanden, daher sind die Bemühungen zur Herstellung des M10-Standards (182 mm) eine fortlaufende Anstrengung. Wie bei einem Halbleiter-Cousin ist die Kostensenkung der Haupttreiber, obwohl die Reinheitsanforderungen völlig unterschiedlich sind.

Vorgeschlagener 450 mm Übergang

Trotz der möglichen Produktivitätsverbesserung besteht ein erheblicher Widerstand gegen den 450-mm-Übergang, da Bedenken hinsichtlich einer unzureichenden Kapitalrendite bestehen. Es gibt auch Probleme im Zusammenhang mit einer erhöhten Variation des Wafers zwischen Chip und Kante zu Kante und zusätzlichen Kantendefekten. 450-mm-Wafer kosten voraussichtlich das Vierfache von 300-mm-Wafern, und die Ausrüstungskosten werden voraussichtlich um 20 bis 50% steigen. Höhere Kosten für die Halbleiterherstellung für größere Wafer erhöhen die Kosten für 450-mm-Fabriken (Halbleiterfertigungsanlagen oder Fabriken). Der Lithograf Chris Mack behauptete 2012, dass der Gesamtpreis pro Chip für 450-mm-Wafer im Vergleich zu 300-mm-Wafern nur um 10–20% gesenkt würde, da über 50% der gesamten Waferbearbeitungskosten lithografisch bedingt sind. Die Umstellung auf größere 450-mm-Wafer würde den Preis pro Chip nur für Prozessvorgänge wie Ätzen reduzieren, bei denen die Kosten mit der Anzahl der Wafer und nicht mit der Waferfläche zusammenhängen. Die Kosten für Verfahren wie die Lithographie sind proportional zur Waferfläche, und größere Wafer würden den Lithographiebeitrag zu den Chipkosten nicht verringern. Nikon plante die Lieferung von 450-mm-Lithografieausrüstungen im Jahr 2015 und die Serienproduktion im Jahr 2017. Im November 2013 stellte ASML die Entwicklung von 450-mm-Lithografieausrüstungen ein und verwies auf den ungewissen Zeitpunkt der Nachfrage nach Chipherstellern.

Die Zeitleiste für 450 mm wurde nicht festgelegt. Im Jahr 2012 wurde erwartet, dass die 450-mm-Produktion im Jahr 2017 beginnen würde, was jedoch nie realisiert wurde. Mark Durcan, damals CEO von Micron Technology , sagte im Februar 2014, dass er davon ausgeht, dass sich die Einführung von 450 mm auf unbestimmte Zeit verzögert oder eingestellt wird. "Ich bin nicht davon überzeugt, dass 450 mm jemals passieren werden, aber in dem Maße, in dem dies der Fall ist, ist es ein langer Weg in die Zukunft. Es besteht für Micron zumindest in den nächsten fünf Jahren keine große Notwendigkeit, a auszugeben viel Geld für 450 mm. Es gibt eine Menge Investitionen, die in die Geräte-Community getätigt werden müssen, um dies zu erreichen. Und der Wert am Ende des Tages - damit die Kunden diese Geräte kaufen würden - halte ich für zweifelhaft. " Ab März 2014 rechnete die Intel Corporation mit einer Bereitstellung von 450 mm bis 2020 (bis zum Ende dieses Jahrzehnts). Mark LaPedus von semiengineering.com berichtete Mitte 2014, dass die Chiphersteller die Einführung von 450 mm "auf absehbare Zeit" verzögert hätten. Laut diesem Bericht erwarteten einige Beobachter 2018 bis 2020, während G. Dan Hutcheson, Geschäftsführer von VLSI Research, erst 2020 bis 2025 450-mm-Fabriken in Produktion gehen sah.

Der Schritt auf 300 mm erforderte große Änderungen, wobei vollautomatische Fabriken 300-mm-Wafer im Vergleich zu kaum automatisierten Fabriken für 200-mm-Wafer verwendeten, teilweise weil eine FOUP für 300-mm-Wafer etwa 7,5 kg wiegt, wenn sie mit 25 300-mm-Wafern beladen ist, in denen ein SMIF vorhanden ist Wiegt etwa 4,8 Kilogramm, wenn es mit 25 200-mm-Wafern beladen wird, was die doppelte physische Kraft der Fabrikarbeiter und eine zunehmende Ermüdung erfordert. 300-mm-FOUPs haben Griffe, damit sie noch von Hand bewegt werden können. 450-mm-FOUPs wiegen 45 Kilogramm, wenn sie mit 25 450-mm-Wafern beladen sind. Daher sind Krane erforderlich, um die FOUPs manuell zu handhaben, und Griffe sind in der FOUP nicht mehr vorhanden. FOUPs werden mit Materialtransportsystemen von Muratec oder Daifuku bewegt . Diese großen Investitionen wurden in den wirtschaftlichen Abschwung nach der Dotcom-Blase getätigt , was zu einem enormen Widerstand gegen eine Aufrüstung auf 450 mm innerhalb des ursprünglichen Zeitrahmens führte. Auf der Rampe bis zu 450 mm sind die Kristallbarren dreimal schwerer (Gesamtgewicht pro Tonne) und das Abkühlen dauert zwei- bis viermal länger, und die Prozesszeit ist doppelt so hoch. Insgesamt erfordert die Entwicklung von 450-mm-Wafern einen erheblichen Engineering-, Zeit- und Kostenaufwand.

Analytische Schätzung der Werkzeuganzahl

Um die Kosten pro Chip zu minimieren , möchten die Hersteller die Anzahl der Chips maximieren, die aus einem einzelnen Wafer hergestellt werden können. Chips haben aufgrund der Beschränkung des Wafer-Würfelns immer eine quadratische oder rechteckige Form . Im Allgemeinen ist dies ein rechnerisch komplexes Problem ohne analytische Lösung, das sowohl von der Fläche der Matrizen als auch von ihrem Seitenverhältnis (quadratisch oder rechteckig) und anderen Überlegungen wie der Breite der Schreiblinie oder der Sägespur und zusätzlichem Platz abhängt besetzt von Ausrichtungs- und Teststrukturen. Beachten Sie, dass Brutto-DPW-Formeln nur den Waferbereich berücksichtigen, der verloren geht, da er nicht zur Herstellung physisch vollständiger Chips verwendet werden kann. Brutto-DPW-Berechnungen berücksichtigen keine Ertragsverluste aufgrund von Fehlern oder parametrischen Problemen.

Trotzdem kann die Anzahl der Brutto-Chips pro Wafer ( DPW ) ausgehend von der Näherung erster Ordnung oder dem Verhältnis von Wafer zu Chipfläche geschätzt werden.

- ,

Dabei ist der Waferdurchmesser (typischerweise in mm) und die Größe jeder Matrize (mm 2 ) einschließlich der Breite der Ritzlinie (oder im Fall einer Sägespur die Schnittfuge plus eine Toleranz). Diese Formel besagt einfach, dass die Anzahl der Chips, die auf den Wafer passen können, die Fläche des Wafers geteilt durch die Fläche jedes einzelnen Chips nicht überschreiten kann . Das wahre Brutto-DPW im besten Fall wird immer überschätzt, da es den Bereich von teilweise strukturierten Chips umfasst, die nicht vollständig auf der Waferoberfläche liegen (siehe Abbildung). Diese teilweise gemusterten Chips stellen keine vollständigen ICs dar und können daher nicht als Funktionsteile verkauft werden.

Verfeinerungen dieser einfachen Formel fügen typischerweise eine Kantenkorrektur hinzu, um Teilchips an der Kante zu berücksichtigen, die im Allgemeinen bedeutender sind, wenn die Fläche des Chips im Vergleich zur Gesamtfläche des Wafers groß ist. Im anderen Grenzfall (unendlich kleine Chips oder unendlich große Wafer) ist die Kantenkorrektur vernachlässigbar.

Der Korrekturfaktor oder Korrekturterm hat im Allgemeinen eine der von De Vries angegebenen Formen:

- (Flächenverhältnis - Umfang / (diagonale Länge der Matrize))

- oder (Flächenverhältnis skaliert um einen Exponentialfaktor)

- oder (Flächenverhältnis skaliert durch einen Polynomfaktor).

Studien, die diese analytischen Formeln mit Brute-Force- Berechnungsergebnissen vergleichen, zeigen, dass die Formeln über praktische Bereiche von Matrizengrößen und Seitenverhältnissen genauer gemacht werden können, indem die Korrekturkoeffizienten auf Werte über oder unter Eins eingestellt werden und die Linearität ersetzt wird Werkzeugabmessung mit (durchschnittliche Seitenlänge) bei Werkzeugen mit großem Seitenverhältnis:

- oder

- oder .

Kristalline Orientierung

Wafer werden aus Kristallen mit einer regelmäßigen Kristallstruktur gezüchtet , wobei Silizium eine kubische Diamantstruktur mit einem Gitterabstand von 5,430710 Å (0,5430710 nm) aufweist. Beim Schneiden in Wafer wird die Oberfläche in einer von mehreren relativen Richtungen ausgerichtet, die als Kristallorientierungen bekannt sind. Die Ausrichtung wird durch den Miller-Index definiert, wobei (100) oder (111) Flächen für Silizium am häufigsten sind. Die Orientierung ist wichtig, da viele der strukturellen und elektronischen Eigenschaften eines Einkristalls stark anisotrop sind . Ionenimplantationstiefe abhängig von der Kristallorientierung des Wafers, da jede Richtung bietet verschiedene Wege für den Transport. Wafer Spaltung typischerweise tritt nur in wenigen gut definierten Richtungen. Einkerben der Wafer entlang Spaltebenen ermöglicht es leicht in einzelne Chips ( „gewürfelt werden Gesenke “) , so dass die Milliarden von einzelnen Schaltungselemente auf einem durchschnittlichen Wafer in viele einzelne Schaltungen voneinander getrennt werden.

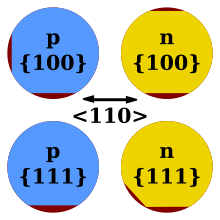

Kristallographische Orientierungskerben

Wafer unter 200 mm Durchmesser haben Wohnungen Schnitt in einer oder mehreren Seiten die Anzeige kristallographischen Ebenen des Wafers (gewöhnlich eine {110} -Fläche). Bei Wafern früherer Generationen vermittelte ein Paar Wohnungen in verschiedenen Winkeln zusätzlich den Dotierungstyp (Konventionen siehe Abbildung). Wafer mit einem Durchmesser von 200 mm und mehr verwenden eine einzelne kleine Kerbe, um die Waferorientierung ohne visuelle Anzeige des Dotierungstyps zu vermitteln.

Dotierung mit Verunreinigungen

Silizium - Wafer sind in der Regel nicht zu 100% reines Silizium, sondern werden mit einer anfänglichen Verunreinigungs gebildet Dotierungskonzentration zwischen 10 13 und 10 16 Atomen pro cm 3 von Bor , Phosphor , Arsen oder Antimon , die zugesetzt wird , um die Schmelze und definiert den Wafer als entweder Bulk-n-Typ oder p-Typ. Verglichen mit der Atomdichte von einkristallinem Silizium von 5 × 10 22 Atomen pro cm 3 ergibt dies jedoch immer noch eine Reinheit von mehr als 99,9999%. Die Wafer können anfänglich auch mit einer gewissen interstitiellen Sauerstoffkonzentration versehen werden. Kohlenstoff- und Metallverunreinigungen werden auf ein Minimum reduziert. Insbesondere Übergangsmetalle müssen für elektronische Anwendungen unter Konzentrationen von Teilen pro Milliarde gehalten werden.

Verbindungshalbleiter

Während Silizium das vorherrschende Material für Wafer ist, die in der Elektronikindustrie verwendet werden, wurden auch andere Materialien der Verbindung III-V oder II-VI verwendet. Galliumarsenid (GaAs), ein nach dem Czochralski-Verfahren hergestellter III-V-Halbleiter , Galliumnitrid (GaN) und Siliziumkarbid (SiC), sind ebenfalls übliche Wafermaterialien, wobei GaN und Saphir in großem Umfang bei der LED- Herstellung verwendet werden.

Siehe auch

Verweise

Externe Links

- Vortrag darüber, wie Silizium zu einem Computerchip verarbeitet wird

- Video des Waferherstellungsprozesses - Eine Videoanleitung zum Waferherstellungsprozess des Waferherstellers Sil'Tronix Silicon Technologies

- Entwicklung des Siliziumwafers durch F450C - Eine Infografik über die Geschichte des Siliziumwafers.