System auf einem Chip - System on a chip

Ein System auf einem Chip ( SoC ; / ˌ ɛ s ˌ oʊ s Ï / ES-oh- SEE oder / s ɒ k / Socke ) ist eine integrierte Schaltung (auch als "Chip" bekannt ist ) , daß alle oder die meisten Komponenten integriert eines Computers oder eines anderen elektronischen Systems . Diese Komponenten umfassen fast immer eine zentrale Verarbeitungseinheit (CPU), Speicher , Ein-/Ausgangsanschlüsse und Sekundärspeicher , oft neben anderen Komponenten wie Funkmodems und einer Grafikverarbeitungseinheit (GPU) – alles auf einem einzigen Substrat oder Mikrochip. Er kann digitale , analoge , Mixed-Signal- und häufig Hochfrequenz- Signalverarbeitungsfunktionen enthalten (andernfalls wird er nur als Anwendungsprozessor betrachtet).

Leistungsstärkere SoCs werden oft mit dedizierten und physisch getrennten Speicher- und Sekundärspeicherchips (fast immer LPDDR und eUFS bzw. eMMC ) gepaart , die in einer sogenannten Package-on-Package- Konfiguration (PoP) über dem SoC angeordnet werden können , oder in der Nähe des SoC platziert werden. Darüber hinaus können SoCs separate drahtlose Modems verwenden.

SoCs stehen im Gegensatz zu der üblichen traditionellen Motherboard- basierten PC- Architektur , die Komponenten nach Funktion trennt und sie über eine zentrale Schnittstellenplatine verbindet. Während ein Motherboard abnehmbare oder austauschbare Komponenten beherbergt und verbindet, integrieren SoCs all diese Komponenten in einen einzigen integrierten Schaltkreis. Ein SoC integriert in der Regel eine CPU, Grafik- und Speicherschnittstellen, Festplatten- und USB-Konnektivität, Direktzugriffs- und Nur-Lese- Speicher und sekundären Speicher und/oder deren Controller auf einem einzigen Schaltungschip, während ein Motherboard diese Module als diskrete Komponenten oder Erweiterungskarten .

Ein SoC integriert einen Mikrocontroller , einen Mikroprozessor oder vielleicht mehrere Prozessorkerne mit Peripheriegeräten wie einer GPU , Wi-Fi und Mobilfunkmodems und/oder einem oder mehreren Coprozessoren . Ähnlich wie ein Mikrocontroller einen Mikroprozessor mit Peripherieschaltungen und Speicher integriert, kann ein SoC als Integration eines Mikrocontrollers mit noch fortschrittlicheren Peripheriegeräten angesehen werden .

Enger integrierte Computersystemdesigns verbessern die Leistung und reduzieren den Energieverbrauch sowie die Halbleiterchipfläche als Multichipdesigns mit äquivalenter Funktionalität. Dies geht auf Kosten einer verringerten Austauschbarkeit von Komponenten. Per Definition ist SoC - Design vollständig oder nahezu vollständig in der verschiedenen Komponenten integriert Module . Aus diesen Gründen gibt es einen allgemeinen Trend zu einer engeren Integration von Komponenten in der Computerhardwareindustrie , teilweise aufgrund des Einflusses von SoCs und der Erfahrungen aus den Märkten für mobile und eingebettete Computer. SoCs können als Teil eines größeren Trends zu Embedded Computing und Hardwarebeschleunigung betrachtet werden .

SoCs sind in den Bereichen Mobile Computing (z. B. in Smartphones und Tablet-Computern ) und Edge-Computing- Märkten weit verbreitet. Sie werden auch häufig in eingebetteten Systemen wie WLAN-Routern und dem Internet der Dinge verwendet .

Typen

Im Allgemeinen gibt es vier unterscheidbare Arten von SoCs:

- SoCs, die um einen Mikrocontroller herum gebaut sind ,

- SoCs, die um einen Mikroprozessor herum gebaut sind und häufig in Mobiltelefonen zu finden sind;

- Spezialisierte anwendungsspezifische integrierte Schaltungs- SoCs, die für bestimmte Anwendungen entwickelt wurden, die nicht in die oben genannten beiden Kategorien passen, und

- Programmierbare SoCs (PSoC), bei denen die meisten Funktionen festgelegt sind, aber einige Funktionen analog zu einem feldprogrammierbaren Gate-Array umprogrammierbar sind .

Anwendungen

SoCs können auf jede Rechenaufgabe angewendet werden. Sie werden jedoch typischerweise im mobilen Computing wie Tablets, Smartphones, Smartwatches und Netbooks sowie eingebetteten Systemen und in Anwendungen verwendet, in denen früher Mikrocontroller verwendet wurden.

Eingebettete Systeme

Wo bisher nur Mikrocontroller eingesetzt werden konnten, gewinnen SoCs im Markt für eingebettete Systeme an Bedeutung. Eine engere Systemintegration bietet eine bessere Zuverlässigkeit und mittlere Zeit zwischen Ausfällen , und SoCs bieten erweiterte Funktionen und Rechenleistung als Mikrocontroller. Die Anwendungen umfassen AI Beschleunigung , Embedded Machine Vision , Datenerfassung, Telemetrie , Vektorverarbeitung und Ambient Intelligence . Embedded SoCs zielen oft auf das Internet der Dinge , das industrielle Internet der Dinge und die Edge-Computing- Märkte ab.

Mobile Computing

Mobile Computing- basierte SoCs bündeln immer Prozessoren, Speicher, On-Chip- Caches , drahtlose Netzwerkfähigkeiten und oft Digitalkamera- Hardware und -Firmware. Mit zunehmender Speichergröße haben High-End-SoCs oft keinen Speicher und Flash-Speicher und stattdessen werden der Speicher und der Flash-Speicher direkt neben oder über dem SoC ( Paket auf Paket ) platziert. Einige Beispiele für mobile Computer-SoCs sind:

- Samsung Electronics : Liste , normalerweise basierend auf ARM

-

Qualcomm :

- Löwenmaul ( Liste ), verwendet in vielen LG- , Xiaomi- , Google Pixel- , HTC- und Samsung Galaxy-Smartphones. Im Jahr 2018 werden Snapdragon-SoCs als Rückgrat von Laptops mit Windows 10 verwendet , die als "Always Connected PCs" vermarktet werden.

Persönliche Computer

Im Jahr 1992 produzierte Acorn Computers die PC-Reihen A3010, A3020 und A4000 mit dem ARM250-SoC. Es kombinierte den ursprünglichen Acorn ARM2-Prozessor mit einem Speichercontroller (MEMC), einem Videocontroller (VIDC) und einem I/O-Controller (IOC). In früheren Acorn ARM- betriebenen Computern waren dies vier diskrete Chips. Der ARM7500-Chip war ihr SoC der zweiten Generation, basierend auf den ARM700-, VIDC20- und IOMD-Controllern, und wurde weithin in eingebetteten Geräten wie Set-Top-Boxen sowie späteren Acorn-Personalcomputern lizenziert.

SoCs Mainstream werden angewendet PCs als 2018. Sie besonders auf angewendet werden Laptops und Tablet - PCs . Tablet- und Laptop-Hersteller haben aus den Embedded-Systemen und Smartphone-Märkten Lehren über einen geringeren Stromverbrauch, bessere Leistung und Zuverlässigkeit durch eine engere Integration von Hardware- und Firmware- Modulen sowie LTE und andere auf dem Chip integrierte drahtlose Netzwerkkommunikation (integrierte Netzwerkschnittstellen-Controller ) gezogen.

ARM- basiert:

- Qualcomm Snapdragon

- ARM250

- ARM7500(FE)

- Apfel M1

x86- basiert:

Struktur

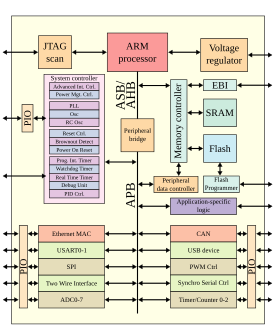

Ein SoC besteht aus Hardware- Funktionseinheiten , einschließlich Mikroprozessoren , die Softwarecode ausführen , sowie einem Kommunikationssubsystem zum Verbinden, Steuern, Direkten und Schnittstellen zwischen diesen Funktionsmodulen.

Funktionskomponenten

Prozessorkerne

Ein SoC muss mindestens einen Prozessorkern haben , aber normalerweise hat ein SoC mehr als einen Kern. Prozessorkerne können ein Mikrocontroller , ein Mikroprozessor (μP), ein digitaler Signalprozessor (DSP) oder ein anwendungsspezifischer Befehlssatzprozessor (ASIP) sein. ASIPs verfügen über Befehlssätze , die für eine Anwendungsdomäne angepasst sind und für eine bestimmte Art von Workload effizienter als Allzweckbefehle sind. Multiprozessor-SoCs haben per Definition mehr als einen Prozessorkern.

Ob Single-Core, Multi-Core oder Manycore , SoC-Prozessorkerne verwenden typischerweise RISC- Befehlssatzarchitekturen. RISC-Architekturen sind gegenüber CISC- Prozessoren für SoCs vorteilhaft, da sie weniger digitale Logik und daher weniger Leistung und Fläche an Bord benötigen , und in den Märkten für eingebettete und mobile Computer sind Fläche und Leistung oft stark eingeschränkt. Insbesondere SoC-Prozessorkerne verwenden häufig die ARM-Architektur, da es sich um einen als IP-Core spezifizierten Soft-Prozessor handelt, der energieeffizienter als x86 ist .

Speicher

SoCs müssen über Halbleiterspeicherblöcke verfügen , um ihre Berechnungen durchzuführen, ebenso wie Mikrocontroller und andere eingebettete Systeme . Abhängig von der Anwendung kann der SoC-Speicher eine Speicherhierarchie und eine Cache-Hierarchie bilden . Auf dem Markt für mobile Computer ist dies üblich, bei vielen eingebetteten Mikrocontrollern mit geringem Stromverbrauch ist dies jedoch nicht erforderlich. Zu den Speichertechnologien für SoCs gehören Read-Only-Memory (ROM), Random Access Memory (RAM), Electrically Erasable Programmable ROM ( EEPROM ) und Flash-Speicher . Wie bei anderen Computersystemen kann RAM in relativ schnellere, aber teurere statische RAM (SRAM) und langsamere, aber billigere dynamische RAM (DRAM) unterteilt werden. Wenn ein SoC eine Cache- Hierarchie hat, wird SRAM normalerweise verwendet, um Prozessorregister und L1-Caches der Kerne zu implementieren, während DRAM für niedrigere Ebenen der Cache-Hierarchie einschließlich des Hauptspeichers verwendet wird . „Hauptspeicher“ kann spezifisch für einen einzigen Prozessor (was sein kann Multi-Core ) , wenn der SOC mehrere Prozessoren verfügt , in welchem Fall es wird Speicher verteilt und muss über geschickt wird § Intermodul- Kommunikations auf dem Chip durch eine andere zugegriffen werden soll , Prozessor. Weitere Informationen zu Speicherproblemen bei mehreren Prozessoren finden Sie unter Cache-Kohärenz und Speicherlatenz .

Schnittstellen

SoCs enthalten externe Schnittstellen , typischerweise für Kommunikationsprotokolle . Diese basieren oft auf Industriestandards wie USB , FireWire , Ethernet , USART , SPI , HDMI , I²C usw. Diese Schnittstellen unterscheiden sich je nach vorgesehener Anwendung. Drahtlose Netzwerkprotokolle wie Wi-Fi , Bluetooth , 6LoWPAN und Nahfeldkommunikation können ebenfalls unterstützt werden.

Bei Bedarf enthalten SoCs analoge Schnittstellen, einschließlich Analog-Digital- und Digital-Analog-Wandler , oft für die Signalverarbeitung . Diese können mit verschiedenen Arten von Sensoren oder Aktoren verbunden werden , einschließlich intelligenter Wandler . Sie können mit anwendungsspezifischen Modulen oder Abschirmungen verbunden werden. Oder sie können sich innerhalb des SoC befinden, beispielsweise wenn ein analoger Sensor in den SoC eingebaut ist und seine Messwerte zur mathematischen Verarbeitung in digitale Signale umgewandelt werden müssen.

Digitale Signalprozessoren

Digitale Signalprozessor (DSP)-Kerne sind oft in SoCs enthalten. Sie führen Signalverarbeitungsoperationen in SoCs für Sensoren , Aktoren , Datenerfassung , Datenanalyse und Multimediaverarbeitung durch. DSP - Kern verfügt typischerweise sehr langes Befehlswort (VLIW) und Single Instruction, Multiple Data (SIMD) Befehlssatzarchitekturen , und ist daher in hohem Maße zugänglich Ausnutzen Befehlsebene Parallelität durch parallele Verarbeitung und superskalare Ausführung . DSP-Kerne weisen meistens anwendungsspezifische Befehle auf und sind als solche typischerweise anwendungsspezifische Befehlssatzprozessoren (ASIP). Solche anwendungsspezifischen Anweisungen entsprechen dedizierten Hardware- Funktionseinheiten, die diese Anweisungen berechnen.

Typische DSP-Befehle umfassen Multiply-Accumulate , Fast Fourier Transformation , Fusion Multiply-Add und Convolutions .

Sonstiges

Wie bei anderen Computersystemen, erfordern SoCs Zeitquellen zu erzeugen Taktsignale , Steuer Ausführung von SoC - Funktionen und Zeitkontext schaffen Signalverarbeitungsanwendungen des SoC, falls erforderlich. Beliebte Zeitquellen sind Quarzoszillatoren und Phasenregelkreise .

SoC- Peripherie einschließlich Zähler- Timer, Echtzeit- Timer und Power-On-Reset- Generatoren. SoCs umfassen auch Spannungsregler und Power-Management- Schaltungen.

Kommunikation zwischen Modulen

SoCs umfassen viele Ausführungseinheiten . Diese Einheiten müssen oft Daten und Anweisungen hin und her senden . Aus diesem Grund benötigen alle SoCs mit Ausnahme der trivialsten Kommunikationssubsysteme . Ursprünglich, wie bei anderen Mikrocomputer - Technologien, Datenbus - Architekturen verwendet wurden, aber vor kurzem Design basierend auf spärlichen Sprechnetzen bekannt als Netzwerke-on-Chip (NoC) hat in dem Vordergrund und werden voraussichtlich zu überholen Bus - Architekturen für SoC - Design in naher Zukunft gestiegen .

Busbasierte Kommunikation

Historisch gesehen verband ein gemeinsam genutzter globaler Computerbus typischerweise die verschiedenen Komponenten, auch "Blöcke" des SoC genannt. Ein sehr gebräuchlicher Bus für die SoC-Kommunikation ist der lizenzgebührenfreie AMBA- Standard (Advanced Microcontroller Bus Architecture ) von ARM .

Controller mit direktem Speicherzugriff leiten Daten direkt zwischen externen Schnittstellen und SoC-Speicher unter Umgehung der CPU oder Steuereinheit weiter , wodurch der Datendurchsatz des SoC erhöht wird . Dies ähnelt einigen Gerätetreibern von Peripheriegeräten auf komponentenbasierten Multi-Chip-Modul- PC-Architekturen.

Computerbusse sind in der Skalierbarkeit eingeschränkt und unterstützen nur bis zu zehn Kerne ( Multicore ) auf einem einzigen Chip. Die Kabelverzögerung ist aufgrund der fortschreitenden Miniaturisierung nicht skalierbar , die Systemleistung skaliert nicht mit der Anzahl der angeschlossenen Kerne, die Betriebsfrequenz des SoC muss mit jedem zusätzlichen angeschlossenen Kern sinken , damit die Stromversorgung nachhaltig ist, und lange Drähte verbrauchen große Mengen an elektrischer Energie. Diese Herausforderungen sind für die Unterstützung von Manycore- Systemen auf dem Chip unerschwinglich .

Netzwerk auf einem Chip

In den späten 2010er Jahren zeichnete sich ein Trend ab, dass SoCs Kommunikationssubsysteme in Form einer netzwerkartigen Topologie anstelle von busbasierten Protokollen implementieren . Ein Trend zu mehr Prozessorkernen auf SoCs hat dazu geführt, dass die Effizienz der On-Chip-Kommunikation zu einem der Schlüsselfaktoren bei der Bestimmung der Gesamtsystemleistung und -kosten geworden ist. Dies hat zur Entstehung von Verbindungsnetzwerken mit Router- basierter Paketvermittlung geführt, die als " Networks on Chip " (NoCs) bekannt sind, um die Engpässe von busbasierten Netzwerken zu überwinden .

Networks-on-chip bietet Vorteile wie ziel- und anwendungsspezifisches Routing , höhere Energieeffizienz und geringere Möglichkeit von Buskonflikten . Network-on-Chip-Architekturen lassen sich von Kommunikationsprotokollen wie TCP und der Internet Protocol Suite für die On-Chip-Kommunikation inspirieren , obwohl sie normalerweise weniger Netzwerkschichten haben . Optimale Network-on-Chip- Netzwerkarchitekturen sind ein ständiges Gebiet von großem Forschungsinteresse. NoC - Architekturen reichen von traditionellen verteilten Rechnernetztopologien wie Torus , hypercube , Maschen und Baum Netzwerke zu genetischem Algorithmus Scheduling zu randomisierten Algorithmen wie Irrfahrten mit Verzweigung und randomisierten Zeit zu Live (TTL).

Viele SoC-Forscher betrachten NoC-Architekturen als die Zukunft des SoC-Designs, da sie nachweislich die Leistungs- und Durchsatzanforderungen von SoC-Designs effizient erfüllen. Aktuelle NoC-Architekturen sind zweidimensional. Das 2D-IC-Design hat begrenzte Auswahlmöglichkeiten bei der Grundrissplanung , da die Anzahl der Kerne in SoCs zunimmt. Wenn also dreidimensionale integrierte Schaltkreise (3DICs) entstehen, suchen SoC-Designer nach dem Aufbau dreidimensionaler On-Chip-Netzwerke, die als 3DNoCs bekannt sind.

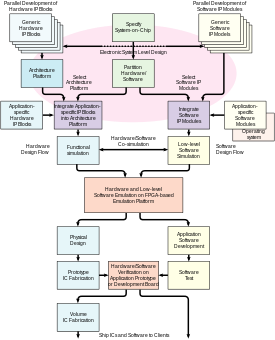

Design-Flow

Ein System auf einem Chip besteht sowohl aus der in § Struktur beschriebenen Hardware als auch aus der Software, die den Mikrocontroller, Mikroprozessor oder digitale Signalprozessorkerne, Peripheriegeräte und Schnittstellen steuert. Der Design-Flow für einen SoC zielt darauf ab, diese Hard- und Software gleichzeitig zu entwickeln, auch bekannt als architektonisches Co-Design. Der Designflow muss auch Optimierungen ( § Optimierungsziele ) und Randbedingungen berücksichtigen .

Die meisten SoCs werden aus vorqualifizierten Hardwarekomponenten- IP-Kernspezifikationen für die oben beschriebenen Hardwareelemente und Ausführungseinheiten , kollektiv "Blöcke", zusammen mit Softwaregerätetreibern entwickelt , die ihren Betrieb steuern können. Von besonderer Bedeutung sind die Protokollstacks , die branchenübliche Schnittstellen wie USB ansteuern . Die Hardwareblöcke werden mit computergestützten Entwurfswerkzeugen zusammengestellt , insbesondere mit elektronischen Entwurfsautomatisierungswerkzeugen ; Die Integration der Softwaremodule erfolgt über eine softwareintegrierte Entwicklungsumgebung .

SoCs-Komponenten werden auch oft in höheren Programmiersprachen wie C++ , MATLAB oder SystemC entworfen und durch High-Level-Synthese- (HLS)-Tools wie C to HDL oder Flow to HDL in RTL- Designs umgewandelt . HLS-Produkte, die als "algorithmische Synthese" bezeichnet werden, ermöglichen es Designern, C++ zu verwenden, um System-, Schaltungs-, Software- und Verifikationsebenen zu modellieren und zu synthetisieren, alles in einer Hochsprache, die Computeringenieuren allgemein bekannt ist, unabhängig von Zeitskalen, die normalerweise in HDL spezifiziert sind. Andere Komponenten können Software bleiben und kompiliert und auf Soft-Core-Prozessoren eingebettet werden, die im SoC als Module in HDL als IP-Cores enthalten sind .

Sobald die Architektur des SoC definiert wurde, werden alle neuen Hardwareelemente in einer abstrakten Hardwarebeschreibungssprache namens Register Transfer Level (RTL) geschrieben, die das Schaltungsverhalten definiert, oder aus einer High-Level-Sprache durch High-Level-Synthese in RTL synthetisiert. Diese Elemente werden in einer Hardwarebeschreibungssprache miteinander verbunden, um das vollständige SoC-Design zu erstellen. Die Logik, die zum Verbinden dieser Komponenten und zum Konvertieren zwischen möglicherweise verschiedenen Schnittstellen von verschiedenen Anbietern angegeben ist, wird als Glue-Logik bezeichnet .

Designüberprüfung

Chips werden auf ihre Validierungskorrektheit überprüft, bevor sie an eine Halbleitergießerei geschickt werden . Dieser Prozess wird als funktionale Verifikation bezeichnet und macht einen erheblichen Teil des Zeit- und Energieaufwands im Chip-Design-Lebenszyklus aus , der oft mit 70 % angegeben wird. Mit der wachsenden Komplexität von Chips werden Hardware-Verifizierungssprachen wie SystemVerilog , SystemC , e und OpenVera verwendet. Bugs in der Verifikationsstufe gefunden wird den Designer berichtet.

Traditionell haben Ingenieure Simulationsbeschleunigung, Emulation oder Prototyping auf umprogrammierbarer Hardware eingesetzt , um Hardware und Software für SoC-Designs vor der Fertigstellung des Designs, bekannt als Tape-Out, zu verifizieren und zu debuggen . Feldprogrammierbare Gate-Arrays (FPGAs) werden für das Prototyping von SoCs bevorzugt, da FPGA-Prototypen umprogrammierbar sind, Debugging ermöglichen und flexibler als anwendungsspezifische integrierte Schaltkreise (ASICs) sind.

Mit hoher Kapazität und schneller Kompilierungszeit sind Simulationsbeschleunigung und Emulation leistungsstarke Technologien, die einen umfassenden Einblick in die Systeme bieten. Beide Technologien arbeiten jedoch langsam, in der Größenordnung von MHz, was erheblich langsamer sein kann – bis zu 100-mal langsamer – als die Betriebsfrequenz des SoC. Beschleunigungs- und Emulationsboxen sind mit über 1 Million US-Dollar ebenfalls sehr groß und teuer.

Im Gegensatz dazu verwenden FPGA-Prototypen FPGAs direkt, um es Ingenieuren zu ermöglichen, mit realen Stimuli bei oder nahe der vollen Betriebsfrequenz eines Systems zu validieren und zu testen. Tools wie Certus werden verwendet, um Sonden in das FPGA-RTL einzufügen, die Signale für die Beobachtung zur Verfügung stellen. Dies wird verwendet, um Hardware-, Firmware- und Software-Interaktionen über mehrere FPGAs hinweg mit ähnlichen Fähigkeiten wie ein Logikanalysator zu debuggen.

Parallel dazu werden die Hardwareelemente gruppiert und durch einen Prozess der Logiksynthese geleitet , bei dem Leistungsbeschränkungen, wie etwa Betriebsfrequenz und erwartete Signalverzögerungen, angewendet werden. Dies erzeugt eine Ausgabe, die als Netzliste bekannt ist und das Design als physikalische Schaltung und ihre Verbindungen beschreibt. Diese Netzlisten werden mit der Glue-Logik kombiniert, die die Komponenten verbindet, um die schematische Beschreibung des SoC als Schaltung zu erstellen, die auf einen Chip gedruckt werden kann. Dieser Vorgang wird als Place and Route bezeichnet und geht dem Tape-Out voraus , falls die SoCs als anwendungsspezifische integrierte Schaltungen (ASIC) hergestellt werden.

Optimierungsziele

SoCs müssen den Stromverbrauch , die Fläche auf dem Chip , die Kommunikation, die Positionierung für die Lokalität zwischen modularen Einheiten und andere Faktoren optimieren . Optimierung ist notwendigerweise ein Designziel von SoCs. Wäre eine Optimierung nicht notwendig, würden die Ingenieure eine Multi-Chip-Modularchitektur verwenden, ohne die Flächenauslastung, den Stromverbrauch oder die Leistung des Systems in gleichem Maße zu berücksichtigen.

Es folgen allgemeine Optimierungsziele für SoC-Designs mit Erläuterungen zu jedem. Im Allgemeinen kann die Optimierung einer dieser Größen ein schwieriges kombinatorisches Optimierungsproblem sein und kann tatsächlich ziemlich leicht NP-hart sein . Daher sind oft ausgeklügelte Optimierungsalgorithmen erforderlich und es kann in einigen Fällen praktisch sein, Näherungsalgorithmen oder Heuristiken zu verwenden. Darüber hinaus enthalten die meisten SoC-Designs mehrere Variablen zur gleichzeitigen Optimierung , sodass im SoC-Design nach effizienten Pareto- Lösungen gesucht wird. Oftmals stehen die Ziele der Optimierung einiger dieser Größen direkt im Widerspruch, was die Designoptimierung von SoCs noch komplizierter macht und Kompromisse beim Systemdesign einführt.

Eine breitere Abdeckung von Kompromissen und Anforderungsanalysen finden Sie unter Requirements Engineering .

Ziele

Energieverbrauch

SoCs sind optimiert, um die elektrische Leistung zu minimieren, die zum Ausführen der Funktionen des SoCs verwendet wird. Die meisten SoCs müssen wenig Strom verbrauchen. SoC-Systeme erfordern oft eine lange Batterielebensdauer (wie Smartphones ), können möglicherweise Monate oder Jahre ohne Stromquelle verbringen, um die autonome Funktion aufrechtzuerhalten, und sind häufig im Stromverbrauch durch eine hohe Anzahl von eingebetteten SoCs begrenzt, die in einem Bereich miteinander vernetzt sind. Darüber hinaus können die Energiekosten hoch sein und das Einsparen von Energie senkt die Gesamtbetriebskosten des SoC. Schließlich kann Abwärme durch hohen Energieverbrauch andere Schaltungskomponenten beschädigen, wenn zu viel Wärme abgeführt wird, was einen weiteren pragmatischen Grund zum Energiesparen darstellt. Die Menge an Energie in einer Schaltung verwendet wird , ist das Integral der Leistung über die Zeit verbraucht wird , und die Durchschnittsrate des Energieverbrauchs ist das Produkt aus Strom durch Spannung . Entsprechend ist die Leistung nach dem Ohmschen Gesetz Strom zum Quadrat mal Widerstand oder Spannung zum Quadrat geteilt durch Widerstand :

Leistung pro Watt

SoCs sind optimiert, um die Energieeffizienz in Leistung pro Watt zu maximieren: Maximieren Sie die Leistung des SoCs bei einem gegebenen Energieverbrauchsbudget. Viele Anwendungen wie Edge Computing , verteilte Verarbeitung und Umgebungsintelligenz erfordern ein gewisses Maß an Rechenleistung , aber die Leistung ist in den meisten SoC-Umgebungen begrenzt. Die ARM-Architektur hat eine höhere Leistung pro Watt als x86 in Embedded-Systemen und wird daher für die meisten SoC-Anwendungen, die einen eingebetteten Prozessor erfordern, gegenüber x86 bevorzugt .

Abwärme

SoC - Designs sind so optimiert , minimieren Abwärme Ausgang auf dem Chip. Wie bei anderen integrierten Schaltkreisen ist die aufgrund der hohen Leistungsdichte erzeugte Wärme der Flaschenhals für die weitere Miniaturisierung von Komponenten. Die Leistungsdichten von integrierten Hochgeschwindigkeitsschaltungen, insbesondere von Mikroprozessoren und einschließlich SoCs, sind sehr ungleichmäßig geworden. Zu viel Abwärme kann Stromkreise beschädigen und die Zuverlässigkeit des Stromkreises im Laufe der Zeit beeinträchtigen . Hohe Temperaturen und thermische Belastungen wirken sich negativ auf die Zuverlässigkeit, Belastungsmigration , verkürzte mittlere Zeit zwischen Ausfällen , Elektromigration , Drahtbonden , Metastabilität und andere Leistungseinbußen des SoC im Laufe der Zeit aus.

Insbesondere befinden sich die meisten SoCs in einem kleinen physischen Bereich oder Volumen, und daher werden die Auswirkungen der Abwärme verstärkt, da sie nur wenig Raum für die Diffusion aus dem System hat. Aufgrund der hohen Anzahl an Transistoren bei modernen Geräten aufgrund des Mooreschen Gesetzes ist oft ein Layout mit ausreichendem Durchsatz und hoher Transistordichte physikalisch durch Herstellungsverfahren realisierbar , würde jedoch zu unannehmbar hohen Wärmemengen im Schaltungsvolumen führen.

Diese thermischen Effekte zwingen SoC- und andere Chipdesigner dazu, konservative Designspielräume anzuwenden , wodurch weniger leistungsfähige Geräte entstehen, um das Risiko eines katastrophalen Ausfalls zu mindern . Aufgrund der erhöhten Transistordichten mit kleiner werdenden Längenskalen erzeugt jede Prozessgeneration mehr Wärmeleistung als die letzte. Erschwerend kommt hinzu, dass SoC-Architekturen in der Regel heterogen sind und räumlich inhomogene Wärmeströme erzeugen , die durch eine gleichmäßige passive Kühlung nicht effektiv abgeschwächt werden können .

Durchsatz

SoCs werden optimiert , um zu maximieren Rechen- und Kommunikations Durchsatz .

Latenz

SoCs sind optimiert, um die Latenz für einige oder alle ihrer Funktionen zu minimieren . Dies kann erreicht werden, indem Elemente mit geeigneter Nähe und Lokalität zueinander angeordnet werden, um die Verbindungsverzögerungen zu minimieren und die Geschwindigkeit zu maximieren, mit der Daten zwischen Modulen, Funktionseinheiten und Speichern übertragen werden. Im Allgemeinen ist die Optimierung zur Minimierung der Latenz ein NP-vollständiges Problem, das dem booleschen Erfüllbarkeitsproblem äquivalent ist .

Bei Aufgaben, die auf Prozessorkernen ausgeführt werden, können Latenz und Durchsatz mit der Aufgabenplanung verbessert werden . Einige Tasks werden jedoch in anwendungsspezifischen Hardwareeinheiten ausgeführt, und selbst die Taskplanung reicht möglicherweise nicht aus, um alle softwarebasierten Tasks zu optimieren, um Zeit- und Durchsatzbeschränkungen zu erfüllen.

Methoden

Systeme auf dem Chip werden mit Standard-Hardware- Verifikations- und -Validierungstechniken modelliert , aber zusätzliche Techniken werden verwendet, um SoC-Entwurfsalternativen zu modellieren und zu optimieren, um das System in Bezug auf die Entscheidungsanalyse mit mehreren Kriterien bezüglich der obigen Optimierungsziele optimal zu machen .

Aufgabenplanung

Die Aufgabenplanung ist eine wichtige Aktivität in jedem Computersystem mit mehreren Prozessen oder Threads, die sich einen einzigen Prozessorkern teilen. Es ist wichtig, die Latenz zu reduzieren und den Durchsatz für eingebettete Software zu erhöhen, die auf den Prozessorkernen eines SoC ausgeführt wird . Nicht jede wichtige Rechenaktivität in einem SoC wird in Software ausgeführt, die auf On-Chip-Prozessoren ausgeführt wird, aber die Planung kann die Leistung softwarebasierter Aufgaben und anderer Aufgaben mit gemeinsam genutzten Ressourcen drastisch verbessern .

SoCs planen Aufgaben häufig gemäß Netzwerkplanung und randomisierten Planungsalgorithmen .

Rohrleitungen

Hardware- und Software-Aufgaben werden beim Prozessordesign häufig in einer Pipeline ausgeführt . Pipelining ist ein wichtiges Prinzip zur Beschleunigung in der Computerarchitektur . Sie werden häufig in GPUs ( Graphics Pipeline ) und RISC-Prozessoren (Weiterentwicklungen der klassischen RISC-Pipeline ) eingesetzt, finden aber auch Anwendung bei anwendungsspezifischen Aufgaben wie der digitalen Signalverarbeitung und Multimedia-Manipulationen im Kontext von SoCs.

Probabilistische Modellierung

SoCs werden oft durch probabilistische Modelle , Warteschlangentheorie, Warteschlangennetzwerke und Markov-Ketten analysiert . Zum Beispiel erlaubt das Little-Gesetz, dass SoC-Zustände und NoC-Puffer als Ankunftsprozesse modelliert und durch Poisson-Zufallsvariablen und Poisson-Prozesse analysiert werden .

Markov-Ketten

SoCs werden oft mit Markov-Ketten modelliert , sowohl zeitdiskrete als auch zeitkontinuierliche Varianten. Die Modellierung der Markov-Kette ermöglicht eine asymptotische Analyse der stationären Verteilung von Leistung, Wärme, Latenz und anderen Faktoren des SoC , um Designentscheidungen für den allgemeinen Fall zu optimieren.

Herstellung

SoC - Chips werden typischerweise hergestellt unter Verwendung von Metall-Oxid-Halbleiter (MOS) -Technologie. Die oben beschriebenen Netzlisten werden als Grundlage für den physischen Entwurfsfluss ( Ort und Route ) verwendet, um die Absicht der Designer in das Design des SoCs umzusetzen. Während dieses Umwandlungsprozesses wird das Design mit statischer Timing-Modellierung, Simulation und anderen Werkzeugen analysiert, um sicherzustellen, dass es die spezifizierten Betriebsparameter wie Frequenz, Leistungsaufnahme und Verlustleistung, Funktionsintegrität (wie im Code der Registerübertragungsebene beschrieben) und elektrische Integrität.

Wenn alle bekannten Fehler behoben und diese erneut überprüft wurden und alle physischen Designprüfungen durchgeführt wurden, werden die physischen Designdateien, die jede Schicht des Chips beschreiben, an die Maskenwerkstatt der Gießerei gesendet, wo ein vollständiger Satz lithografischer Glasmasken geätzt wird . Diese werden an eine Wafer-Fertigungsanlage geschickt, um die SoC-Chips vor dem Verpacken und Testen zu erstellen.

SoCs können mit verschiedenen Technologien hergestellt werden, darunter:

ASICs verbrauchen weniger Strom und sind schneller als FPGAs, können jedoch nicht umprogrammiert werden und sind teuer in der Herstellung. FPGA-Designs eignen sich eher für Designs mit geringerer Stückzahl, aber nach genügend Produktionseinheiten reduzieren ASICs die Gesamtbetriebskosten.

SoC-Designs verbrauchen weniger Strom und sind kostengünstiger und zuverlässiger als die Multi-Chip-Systeme, die sie ersetzen. Mit weniger Paketen im System werden auch die Montagekosten reduziert.

Wie bei den meisten Designs mit sehr großer Integration (VLSI) sind jedoch die Gesamtkosten für einen großen Chip höher als für die gleiche Funktionalität, die auf mehrere kleinere Chips verteilt ist, aufgrund geringerer Ausbeuten und höherer einmaliger Engineering- Kosten.

Wenn es nicht möglich ist, einen SoC für eine bestimmte Anwendung zu konstruieren, ist eine Alternative ein System in Package (SiP), das eine Anzahl von Chips in einem einzigen Package umfasst . Bei großen Stückzahlen ist SoC kostengünstiger als SiP, da die Verpackung einfacher ist. Ein weiterer Grund, warum SiP bevorzugt werden kann, besteht darin, dass die Abwärme in einem SoC für einen bestimmten Zweck zu hoch sein kann, weil die Funktionskomponenten zu nahe beieinander liegen, und in einem SiP wird die Wärme von verschiedenen Funktionsmodulen besser abgeleitet, da sie physikalisch weiter voneinander entfernt sind.

Benchmarks

Die Forschung und Entwicklung von SoCs vergleicht oft viele Optionen. Benchmarks wie COSMIC werden entwickelt, um solche Bewertungen zu unterstützen.

Siehe auch

- Liste der System-on-a-Chip-Lieferanten

- Post-Silizium-Validierung

- ARM-Architektur

- Single-Board-Computer

- System im Paket

- Netzwerk auf einem Chip

- Programmierbares SoC

- Anwendungsspezifischer Befehlssatzprozessor (ASIP)

- Plattformbasiertes Design

- Lab auf einem Chip

- Organ auf einem Chip in der Biomedizintechnik

- Multi-Chip-Modul

- Liste der Qualcomm Snapdragon-Prozessoren - Qualcomm

- Exynos - Samsung

Anmerkungen

Verweise

Weiterlesen

- Badawy, Wael; Jullien, Graham A., Hrsg. (2003). System-on-Chip für Echtzeitanwendungen . Kluwer International Series in Engineering and Computer Science, SECS 711. Boston: Kluwer Academic Publishers . ISBN 9781402072543. OCLC 50478525 . 465 Seiten.

- Furber, Stephen B. (2000). ARM-System-on-Chip-Architektur . Boston: Addison-Wesley. ISBN 0-201-67519-6.

- Kundu, Santanu; Chattopadhyay, Santanu (2014). Network-on-Chip: die nächste Generation der System-on-Chip-Integration (1. Aufl.). Boca Raton, FL: CRC-Presse. ISBN 9781466565272. OCLC 895661009 .

Externe Links

- SOCC Jährliche IEEE Internationale SoC-Konferenz

- Baya- freies SoC-Plattform-Assembly- und IP-Integrationstool

- Systems on Chip for Embedded Applications , Auburn University Seminar in VLSI

- Instant SoC SoC für FPGAs definiert durch C++