Zeitstempelzähler - Time Stamp Counter

Der Time Stamp Counter ( TSC ) ist ein 64-Bit- Register , das auf allen x86- Prozessoren seit dem Pentium vorhanden ist . Es zählt die Anzahl der CPU- Zyklen seit seinem Zurücksetzen. Der Befehl RDTSCgibt den TSC in EDX:EAX zurück. Löscht im x86-64- Modus RDTSCauch die oberen 32 Bit von RAX und RDX . Sein Opcode ist 0F 31. Pentium- Konkurrenten wie der Cyrix 6x86 hatten nicht immer einen TSC und können als RDTSCillegale Anweisung betrachtet werden. Cyrix hat ihrem MII einen Zeitstempelzähler hinzugefügt .

Benutzen

Der Zeitstempelzähler war einst eine hervorragende Möglichkeit für ein Programm mit hoher Auflösung und geringem Overhead, CPU-Timing-Informationen zu erhalten. Mit dem Aufkommen von Multi-Core- / Hyper-Thread- CPUs, Systemen mit mehreren CPUs und Betriebssystemen im Ruhezustand kann man sich nicht darauf verlassen, dass der TSC genaue Ergebnisse liefert – es sei denn, es wird große Sorgfalt darauf verwendet, die möglichen Fehler zu beheben: Tickrate und ob alle Kerne (Prozessoren) haben identische Werte in ihren Zeiterfassungsregistern. Es gibt keine Zusage, dass die Zeitstempelzähler mehrerer CPUs auf einem einzigen Motherboard synchronisiert werden. Daher kann ein Programm nur dann zuverlässige Ergebnisse erzielen, wenn es sich auf die Ausführung auf einer bestimmten CPU beschränkt. Selbst dann kann sich die CPU-Geschwindigkeit aufgrund von Energiesparmaßnahmen des Betriebssystems oder BIOS ändern , oder das System kann in den Ruhezustand versetzt und später wieder aufgenommen werden, wodurch der TSC zurückgesetzt wird. In diesen letzteren Fällen muss das Programm den Zähler regelmäßig neu kalibrieren, um relevant zu bleiben.

Das Vertrauen auf den TSC verringert auch die Portabilität, da andere Prozessoren möglicherweise nicht über eine ähnliche Funktion verfügen. Neuere Intel-Prozessoren enthalten einen TSC mit konstanter Rate (identifiziert durch das kern.timecounter.invariant_tsc sysctl auf FreeBSD oder durch das constant_tscFlag " " in Linux /proc/cpuinfo). Bei diesen Prozessoren tickt der TSC mit der Nennfrequenz des Prozessors, unabhängig von der tatsächlichen CPU-Taktfrequenz aufgrund von Turbo- oder Energiesparzuständen. Daher zählen TSC-Ticks den Zeitablauf, nicht die Anzahl der verstrichenen CPU-Taktzyklen.

Auf Windows-Plattformen rät Microsoft aus genau diesen Gründen dringend davon ab, den TSC für hochauflösendes Timing zu verwenden, und stellt stattdessen die Windows-APIs QueryPerformanceCounter und QueryPerformanceFrequency. Auf POSIX- Systemen kann ein Programm eine ähnliche Funktion erhalten, indem es den Wert der CLOCK_MONOTONIC_RAWUhr mithilfe der clock_gettimeFunktion liest .

Beginnend mit dem Pentium Pro haben Intel-Prozessoren die Ausführung außerhalb der Reihenfolge geübt , bei der Anweisungen nicht unbedingt in der Reihenfolge ausgeführt werden, in der sie im Programm erscheinen. Dies kann dazu führen, dass der Prozessor RDTSCfrüher ausgeführt wird, als ein einfaches Programm erwartet, was zu einer irreführenden Zykluszählung führt. Der Programmierer kann dieses Problem lösen, indem er einen Serialisierungsbefehl wie etwa CPUID einfügt , um den Abschluss jedes vorhergehenden Befehls zu erzwingen, bevor das Programm fortgesetzt werden kann. Der RDTSCPBefehl ist eine Variante davon RDTSC, die eine teilweise Serialisierung des Befehlsstroms bietet, aber nicht als Serialisierung betrachtet werden sollte.

Implementierung in verschiedenen Prozessoren

Intel-Prozessorfamilien erhöhen den Zeitstempelzähler unterschiedlich:

- Für Pentium M- Prozessoren (Familie [06H], Modelle [09H, 0DH]); für Pentium 4-Prozessoren Intel Xeon- Prozessoren (Familie [0FH], Modelle [00H, 01H oder 02H]); und für Prozessoren der P6-Familie: Der Zeitstempelzähler inkrementiert mit jedem internen Prozessortaktzyklus. Der interne Prozessortakt wird durch das aktuelle Verhältnis von Kerntakt zu Bustakt bestimmt. Übergänge zur Intel SpeedStep-Technologie können sich auch auf den Prozessortakt auswirken.

- Für Pentium 4- Prozessoren, Intel Xeon-Prozessoren (Familie [0FH], Modelle [03H und höher]); für Intel Core Solo- und Intel Core Duo- Prozessoren (Familie [06H], Modell [0EH]); für die Intel Xeon Prozessor 5100 Serie und Intel Core 2 Duo Prozessoren (Familie [06H], Modell [0FH]); für Intel Core 2 und Intel Xeon Prozessoren (Familie [06H], Display_Modell [17H]); für Intel Atom Prozessoren (Familie [06H], display_model [1CH]): Der Zeitstempelzähler erhöht sich mit konstanter Geschwindigkeit. Diese Rate kann durch das maximale Verhältnis von Kerntakt zu Bustakt des Prozessors oder durch die maximale Auflösungsfrequenz, mit der der Prozessor gebootet wird, eingestellt werden. Die maximal aufgelöste Frequenz kann von der maximal qualifizierten Frequenz des Prozessors abweichen.

Die spezifische Prozessorkonfiguration bestimmt das Verhalten. Ein konstantes TSC-Verhalten stellt sicher, dass die Dauer jedes Taktticks gleich ist und ermöglicht die Verwendung des TSC als Wanduhr-Timer, selbst wenn der Prozessorkern die Frequenz ändert. Dies ist das Architekturverhalten für alle späteren Intel-Prozessoren.

AMD-Prozessoren bis zum K8- Kern haben den Zeitstempelzähler immer bei jedem Taktzyklus inkrementiert. So konnten die Energieverwaltungsfunktionen die Anzahl der Inkremente pro Sekunde ändern, und die Werte konnten zwischen verschiedenen Kernen oder Prozessoren im selben System nicht mehr synchron sein. Für Windows bietet AMD ein Dienstprogramm zum regelmäßigen Synchronisieren der Zähler auf Mehrkern-CPUs. AMD-Chips verfügen seit der Familie 10h (Barcelona/Phenom) über einen konstanten TSC, der entweder durch die HyperTransport- Geschwindigkeit oder den höchsten P-Zustand angesteuert werden kann . Ein CPUID- Bit ( Fn8000_0007:EDX_8) gibt dies bekannt; Intel-CPUs melden auch ihren invarianten TSC auf diesem Bit.

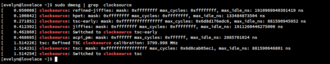

Verwendung des Betriebssystems

Ein Betriebssystem kann Methoden bereitstellen, die die RDTSCAnweisung für die Zeitmessung unter der Kontrolle des Administrators sowohl verwenden als auch nicht verwenden . Beispielsweise deaktiviert der seccomp-Sandboxing-Modus bei einigen Versionen des Linux- Kernels . Es kann auch mit dem Argument zum Systemaufruf deaktiviert werden .

RDTSCPR_SET_TSCprctl()

Verwendung bei der Ausnutzung von Cache-Seitenkanalangriffen

Der Zeitstempelzähler kann verwendet werden, um Anweisungen genau zu timen, die in den Sicherheitslücken Meltdown und Spectre ausgenutzt werden können . Wenn dies jedoch nicht verfügbar ist, können andere Zähler oder Timer verwendet werden, wie dies bei den ARM- Prozessoren der Fall ist, die für diese Art von Angriff anfällig sind.

Andere Architekturen

Andere Prozessoren haben ebenfalls Register, die CPU-Taktzyklen zählen, jedoch mit anderen Namen. Beim AVR32 wird es beispielsweise als Performance Clock Counter (PCCNT)-Register bezeichnet. SPARC V9 stellt das TICKRegister bereit . PowerPC stellt das 64-Bit- TBRRegister bereit .

ARMv7- und ARMv8- Architekturen bieten einen generischen Zähler, der mit einer konstanten Frequenz zählt. ARMv7 bietet das Cycle Counter Register ( CCNT- Befehl) zum Lesen und Schreiben des Zählers, aber der Befehl ist privilegiert.

Siehe auch

- Hochpräziser Ereignis-Timer (HPET)

Verweise

Externe Links

- cycle.h - C- Code zum Lesen des hochauflösenden Timers auf vielen CPUs und Compilern.

- [1] - Sehr einfacher C- Code zum Auslesen des Timers auf einem x86-Rechner. Dies liest den 64-Bit-Wert in zwei 32-Bit-Ganzzahlen und kombiniert sie - die Verwendung von nur einer 64-Bit-Ganzzahl ist eine weitere Option.

- AMD-Ingenieur über TSC-Drift bei AMD-Prozessoren